From WikiChip

Difference between revisions of "intel/platforms/moorestown"

| Line 23: | Line 23: | ||

| chipset = Langwell | | chipset = Langwell | ||

| chipset 2 = Briertown | | chipset 2 = Briertown | ||

| − | | chipset | + | | chipset 3 = Evans Peak |

| succession = Yes | | succession = Yes | ||

| Line 34: | Line 34: | ||

The Moorestown platform offers 2x reduction in average circuit board size and up to 50x standby power reduction vs {{\\|Menlow}} equivalent. | The Moorestown platform offers 2x reduction in average circuit board size and up to 50x standby power reduction vs {{\\|Menlow}} equivalent. | ||

| + | |||

| + | == Overview == | ||

| + | [[File:moorestown platform.png|650px]] | ||

Revision as of 13:57, 21 April 2017

| Moorestown Platform | |

| Developer | Intel |

| Manufacturer | Intel, TSMC |

| Process | 45 nm 0.045 μm

4.5e-5 mm |

| Technology | CMOS |

| Platform | |

| Cores | Lincroft |

| Chipset | Langwell, Briertown, Evans Peak |

| Succession | |

| ← | → |

| Menlow | Oak Trail |

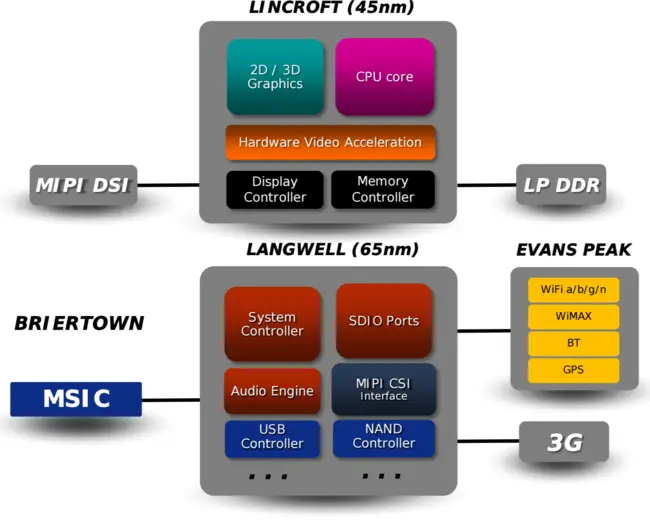

Moorestown is the platform name for Intel's low-power platform Bonnell-based processors and chipsets designed for Mobile Internet Devices (MID) and Ultra Mobile PCs (UMPCs) serving as a successor to Menlow. Moorestown consists of a Lincroft-based processor, the Langwell chipset, and the Briertown Mixed Signal IC (MSIC).

The Moorestown platform offers 2x reduction in average circuit board size and up to 50x standby power reduction vs Menlow equivalent.