-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

Difference between revisions of "intel/chipsets/poulsbo"

< intel

(→Die Shot) |

|||

| Line 34: | Line 34: | ||

== Die Shot == | == Die Shot == | ||

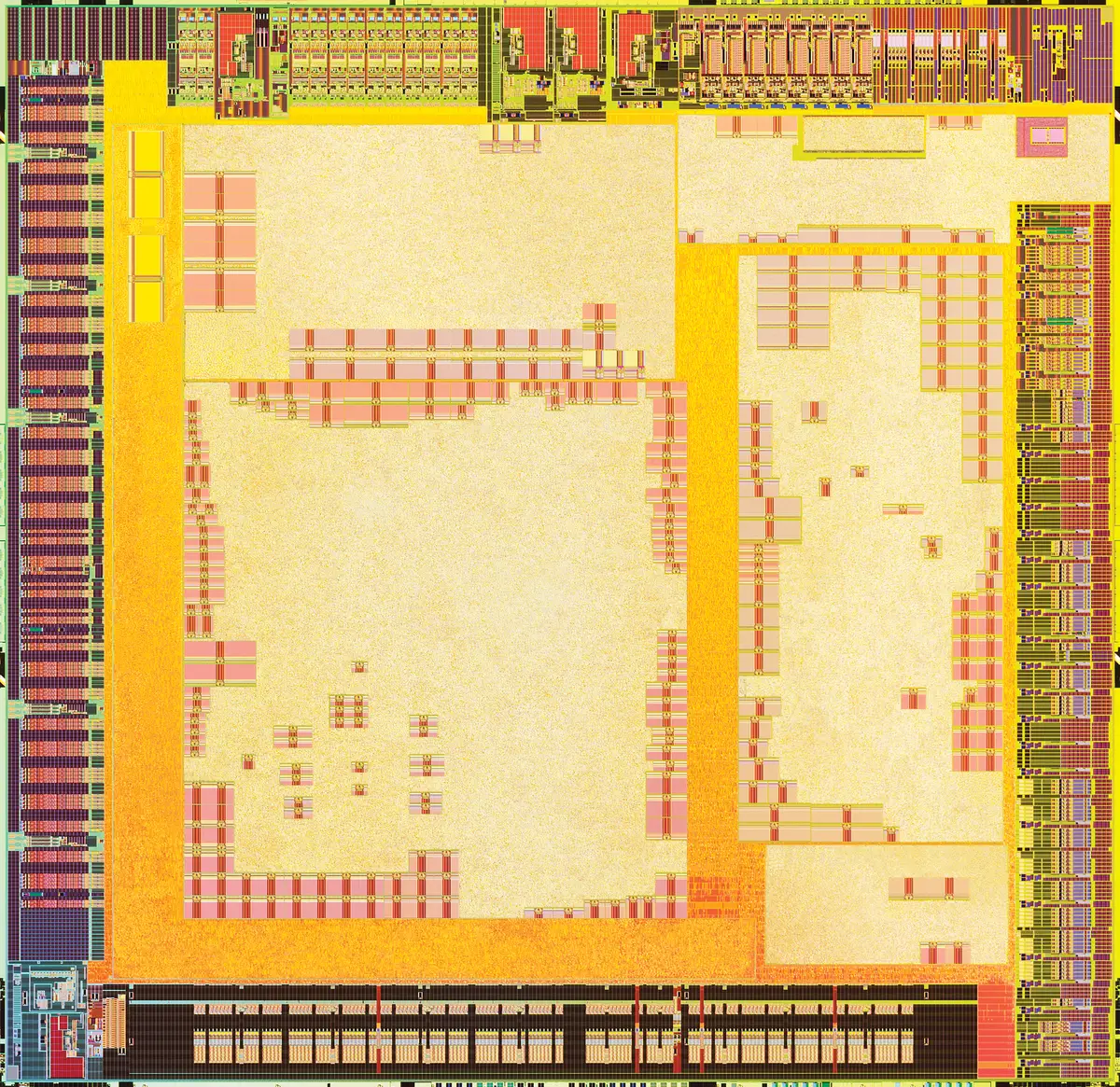

* [[0.13 μm process]] | * [[0.13 μm process]] | ||

| − | [[File:poulsbo die.png| | + | [[File:poulsbo die.png|1200px]] |

Revision as of 20:57, 26 March 2017

Poulsbo is a chipset for Intel's first generation of Atom processors based on the Bonnell microarchitecture.

Overview

| This section is empty; you can help add the missing info by editing this page. |

Die Shot

Hidden category:

Facts about "Poulsbo - Chipsets - Intel"

| bus speed | 533 MHz (0.533 GHz, 533,000 kHz) + |

| bus type | FSB + |

| designer | Intel + and Imagination Technologies + |

| first announced | March 2, 2008 + |

| instance of | chipset + |

| manufacturer | Intel + |

| name | Poulsbo + |

| process | 130 nm (0.13 μm, 1.3e-4 mm) + |

| technology | CMOS + and GTL + |