(Corrected package name.) |

|||

| (11 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{amd title|Ryzen 9 4900HS}} | {{amd title|Ryzen 9 4900HS}} | ||

| − | {{chip}} | + | {{chip |

| − | '''Ryzen 9 4900HS''' is a {{arch|64}} [[octa-core]] high-end performance [[x86]] mobile microprocessor introduced by [[AMD]] in early [[2020]]. Fabricated on [[N7|TSMC's 7-nanometer process]] based on AMD's {{amd|Zen 2|Zen 2 microarchitecture|l=arch}}, the 4900HS operates at a base frequency of 3.0 GHz with a [[TDP]] of 35 W and a {{amd|Precision Boost| | + | |name=Ryzen 9 4900HS |

| + | |no image=No | ||

| + | |designer=AMD | ||

| + | |manufacturer=TSMC | ||

| + | |model number=4900HS | ||

| + | |market=Mobile | ||

| + | |first announced=March 16, 2020 | ||

| + | |first launched=March 16, 2020 | ||

| + | |family=Ryzen 9 | ||

| + | |series=4000 | ||

| + | |locked=Yes | ||

| + | |frequency=3,000 MHz | ||

| + | |turbo frequency=4,300 MHz | ||

| + | |clock multiplier=30 | ||

| + | |isa=x86-64 | ||

| + | |isa family=x86 | ||

| + | |microarch=Zen 2 | ||

| + | |core name=Renoir | ||

| + | |core family=23 | ||

| + | |core model=96 | ||

| + | |core stepping=A1 | ||

| + | |process=7 nm | ||

| + | |transistors=9,800,000,000 | ||

| + | |technology=CMOS | ||

| + | |die area=156 mm² | ||

| + | |word size=64 bit | ||

| + | |core count=8 | ||

| + | |thread count=16 | ||

| + | |max memory=64 GiB | ||

| + | |max cpus=1 | ||

| + | |tdp=35 W | ||

| + | |tcase min=0 °C | ||

| + | |tcase max=105 °C | ||

| + | |package name 1=amd,fp6 | ||

| + | }} | ||

| + | '''Ryzen 9 4900HS''' is a {{arch|64}} [[octa-core]] high-end performance [[x86]] mobile microprocessor introduced by [[AMD]] in early [[2020]]. Fabricated on [[N7|TSMC's 7-nanometer process]] and based on AMD's {{amd|Zen 2|Zen 2 microarchitecture|l=arch}}, the 4900HS operates at a base frequency of 3.0 GHz with a [[TDP]] of 35 W and a {{amd|Precision Boost|boost}} frequency of up to 4.3 GHz. This APU supports up to 64 GiB of DDR4-3200 or up to 32 GiB of quad-channel LPDDR4x-4266 memory. The 4900HS integrates {{amd|Radeon Vega 8}} graphics operating at up to 1.75 GHz. | ||

| + | |||

| + | This processor is a lower-power version of the {{\\|4900H}}, featuring slightly lower base and turbo frequencies. | ||

| + | |||

| + | == Cache == | ||

| + | {{main|amd/microarchitectures/zen 2#Memory_Hierarchy|l1=Zen 2 § Cache}} | ||

| + | {{cache size | ||

| + | |l1 cache=512 KiB | ||

| + | |l1i cache=256 KiB | ||

| + | |l1i break=8x32 KiB | ||

| + | |l1i desc=8-way set associative | ||

| + | |l1d cache=256 KiB | ||

| + | |l1d break=8x32 KiB | ||

| + | |l1d desc=8-way set associative | ||

| + | |l1d policy=write-back | ||

| + | |l2 cache=4 MiB | ||

| + | |l2 break=8x512 KiB | ||

| + | |l2 desc=8-way set associative | ||

| + | |l2 policy=write-back | ||

| + | |l3 cache=8 MiB | ||

| + | |l3 break=2x4 MiB | ||

| + | |l3 desc=16-way set associative | ||

| + | |l3 policy=write-back | ||

| + | }} | ||

| + | |||

| + | == Memory controller == | ||

| + | This SoC features two memory controllers, each supporting DDR4 or LPDDR4x. This chip supports up to 64 GiB of dual-channel DDR4 memory with data rates of up to 3200 MT/s (51.2 GB/s) or up to 32 GiB of quad-channel LPDDR4x with data rates of up to 4266 MT/s (68.27 GB/s). | ||

| + | |||

| + | {{memory controller | ||

| + | |type=DDR4-3200 | ||

| + | |type 2=LPDDR4x-4266 | ||

| + | |max mem=64 GiB | ||

| + | |controllers=2 | ||

| + | |channels=4 | ||

| + | |max bandwidth=68.27 GB/s | ||

| + | |bandwidth schan=17.07 GB/s | ||

| + | |bandwidth dchan=34.13 GB/s | ||

| + | |bandwidth qchan=68.27 GB/s | ||

| + | }} | ||

| + | |||

| + | == Expansions == | ||

| + | This processor has 16 PCIe lanes, 1x8 designated for a discrete [[GPU]], 1x4 additional lanes for storage (e.g., NVMe), and 1x4 additional lanes reserved for additional peripherals (e.g., WiFi or LTE). | ||

| + | |||

| + | {{expansions main | ||

| + | | | ||

| + | {{expansions entry | ||

| + | |type=PCIe | ||

| + | |pcie revision=3.0 | ||

| + | |pcie lanes=16 | ||

| + | |pcie config=1x8+1x4+1x4 | ||

| + | |pcie config 2=2x4+1x4+1x4 | ||

| + | }} | ||

| + | }} | ||

| + | |||

| + | == Graphics == | ||

| + | {{integrated graphics | ||

| + | | gpu = Radeon Vega 8 | ||

| + | | device id = | ||

| + | | designer = AMD | ||

| + | | execution units = 8 | ||

| + | | unified shaders = 512 | ||

| + | | max displays = 4 | ||

| + | | max memory = | ||

| + | | frequency = | ||

| + | | max frequency = 1,750 MHz | ||

| + | |||

| + | | output crt = | ||

| + | | output sdvo = | ||

| + | | output dsi = | ||

| + | | output edp = | ||

| + | | output dp = Yes | ||

| + | | output hdmi = Yes | ||

| + | | output vga = | ||

| + | | output dvi = | ||

| + | |||

| + | | directx ver = | ||

| + | | opengl ver = | ||

| + | | opencl ver = | ||

| + | | hdmi ver = | ||

| + | | dp ver = | ||

| + | | edp ver = | ||

| + | | max res hdmi = | ||

| + | | max res hdmi freq = | ||

| + | | max res dp = | ||

| + | | max res dp freq = | ||

| + | | max res edp = | ||

| + | | max res edp freq = | ||

| + | | max res vga = | ||

| + | | max res vga freq = | ||

| + | }} | ||

| + | {{zen 2 with vega hardware accelerated video table}} | ||

| + | |||

| + | == Features == | ||

| + | {{x86 features | ||

| + | |real=Yes | ||

| + | |protected=Yes | ||

| + | |smm=Yes | ||

| + | |fpu=Yes | ||

| + | |x8616=Yes | ||

| + | |x8632=Yes | ||

| + | |x8664=Yes | ||

| + | |nx=Yes | ||

| + | |mmx=Yes | ||

| + | |emmx=Yes | ||

| + | |sse=Yes | ||

| + | |sse2=Yes | ||

| + | |sse3=Yes | ||

| + | |ssse3=Yes | ||

| + | |sse41=Yes | ||

| + | |sse42=Yes | ||

| + | |sse4a=Yes | ||

| + | |avx=Yes | ||

| + | |avx2=Yes | ||

| + | |avx512f=No | ||

| + | |avx512cd=No | ||

| + | |avx512er=No | ||

| + | |avx512pf=No | ||

| + | |avx512bw=No | ||

| + | |avx512dq=No | ||

| + | |avx512vl=No | ||

| + | |avx512ifma=No | ||

| + | |avx512vbmi=No | ||

| + | |avx5124fmaps=No | ||

| + | |avx512vnni=No | ||

| + | |avx5124vnniw=No | ||

| + | |avx512vpopcntdq=No | ||

| + | |abm=Yes | ||

| + | |tbm=No | ||

| + | |bmi1=Yes | ||

| + | |bmi2=Yes | ||

| + | |fma3=Yes | ||

| + | |fma4=No | ||

| + | |aes=Yes | ||

| + | |rdrand=Yes | ||

| + | |sha=Yes | ||

| + | |xop=No | ||

| + | |adx=Yes | ||

| + | |clmul=Yes | ||

| + | |f16c=Yes | ||

| + | |bfloat16=No | ||

| + | |tbt1=No | ||

| + | |tbt2=No | ||

| + | |tbmt3=No | ||

| + | |bpt=No | ||

| + | |eist=No | ||

| + | |sst=No | ||

| + | |flex=No | ||

| + | |fastmem=No | ||

| + | |ivmd=No | ||

| + | |intelnodecontroller=No | ||

| + | |intelnode=No | ||

| + | |kpt=No | ||

| + | |ptt=No | ||

| + | |intelrunsure=No | ||

| + | |mbe=No | ||

| + | |isrt=No | ||

| + | |sba=No | ||

| + | |mwt=No | ||

| + | |sipp=No | ||

| + | |att=No | ||

| + | |ipt=No | ||

| + | |tsx=No | ||

| + | |txt=No | ||

| + | |ht=No | ||

| + | |vpro=No | ||

| + | |vtx=No | ||

| + | |vtd=No | ||

| + | |ept=No | ||

| + | |mpx=No | ||

| + | |sgx=No | ||

| + | |securekey=No | ||

| + | |osguard=No | ||

| + | |intqat=No | ||

| + | |dlboost=No | ||

| + | |3dnow=No | ||

| + | |e3dnow=No | ||

| + | |smartmp=No | ||

| + | |powernow=No | ||

| + | |amdvi=Yes | ||

| + | |amdv=Yes | ||

| + | |amdsme=No | ||

| + | |amdtsme=No | ||

| + | |amdsev=No | ||

| + | |rvi=No | ||

| + | |smt=Yes | ||

| + | |sensemi=Yes | ||

| + | |xfr=No | ||

| + | |xfr2=No | ||

| + | |mxfr=No | ||

| + | |amdpb=No | ||

| + | |amdpb2=No | ||

| + | |amdpbod=No | ||

| + | }} | ||

| + | |||

| + | == Die == | ||

| + | {{amd renoir die}} | ||

Latest revision as of 23:51, 25 March 2023

| Edit Values | |

| Ryzen 9 4900HS | |

| General Info | |

| Designer | AMD |

| Manufacturer | TSMC |

| Model Number | 4900HS |

| Market | Mobile |

| Introduction | March 16, 2020 (announced) March 16, 2020 (launched) |

| Shop | Amazon |

| General Specs | |

| Family | Ryzen 9 |

| Series | 4000 |

| Locked | Yes |

| Frequency | 3,000 MHz |

| Turbo Frequency | 4,300 MHz |

| Clock multiplier | 30 |

| Microarchitecture | |

| ISA | x86-64 (x86) |

| Microarchitecture | Zen 2 |

| Core Name | Renoir |

| Core Family | 23 |

| Core Model | 96 |

| Core Stepping | A1 |

| Process | 7 nm |

| Transistors | 9,800,000,000 |

| Technology | CMOS |

| Die | 156 mm² |

| Word Size | 64 bit |

| Cores | 8 |

| Threads | 16 |

| Max Memory | 64 GiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| TDP | 35 W |

| Tcase | 0 °C – 105 °C |

| Packaging | |

| Package | FP6 (FC-OBGA) |

| Dimension | 35 mm × 25 mm × 1.38 mm |

| Pitch | 0.65 mm |

| Contacts | 1140 |

Ryzen 9 4900HS is a 64-bit octa-core high-end performance x86 mobile microprocessor introduced by AMD in early 2020. Fabricated on TSMC's 7-nanometer process and based on AMD's Zen 2 microarchitecture, the 4900HS operates at a base frequency of 3.0 GHz with a TDP of 35 W and a boost frequency of up to 4.3 GHz. This APU supports up to 64 GiB of DDR4-3200 or up to 32 GiB of quad-channel LPDDR4x-4266 memory. The 4900HS integrates Radeon Vega 8 graphics operating at up to 1.75 GHz.

This processor is a lower-power version of the 4900H, featuring slightly lower base and turbo frequencies.

Cache[edit]

- Main article: Zen 2 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller[edit]

This SoC features two memory controllers, each supporting DDR4 or LPDDR4x. This chip supports up to 64 GiB of dual-channel DDR4 memory with data rates of up to 3200 MT/s (51.2 GB/s) or up to 32 GiB of quad-channel LPDDR4x with data rates of up to 4266 MT/s (68.27 GB/s).

|

Integrated Memory Controller

|

||||||||||||

|

||||||||||||

Expansions[edit]

This processor has 16 PCIe lanes, 1x8 designated for a discrete GPU, 1x4 additional lanes for storage (e.g., NVMe), and 1x4 additional lanes reserved for additional peripherals (e.g., WiFi or LTE).

Expansion Options |

|||||

|

|||||

Graphics[edit]

|

Integrated Graphics Information

|

||||||||||||||||||

|

||||||||||||||||||

| [Edit] Zen 2 with Radeon Vega Hardware Accelerated Video Capabilities | |||||

|---|---|---|---|---|---|

| Codec | Encode | Decode | |||

| VP9 8bpc/10bpc | 1080p240 4K 60 FPS | ||||

| MPEG-2 (H.262) 8b | 1080p240 4K 60 FPS |

1080p480 4K 120 FPS | |||

| HEVC (H.265) 8bpc/10bpc | 1080p240 4K 60 FPS |

1080p240 4K 60 FPS | |||

Features[edit]

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

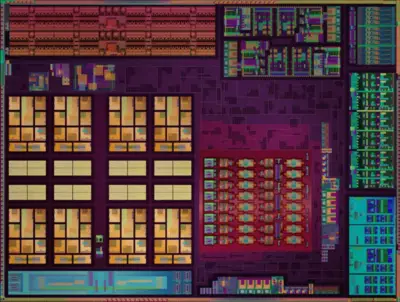

Die[edit]

- Main article: Zen 2 § Die

Renoir microprocessors are fabricated on TSMC's 7-nanometer process. This SoC integrates 9.8 billion transistors on a single 156 mm² monolithic die which includes both the Zen 2 CPU cores along with the Vega GPU and various other additional components.

- 7-nanometer process (N7)

- 9,800,000,000 transistors

- 156 mm² die size

| full page name | amd/ryzen 9/4900hs + |

| instance of | microprocessor + |

| ldate | 1900 + |