From WikiChip

Difference between revisions of "nervana/nnp/nnp-t 1400"

| (2 intermediate revisions by the same user not shown) | |||

| Line 25: | Line 25: | ||

|smp interconnect rate=28 GT/s | |smp interconnect rate=28 GT/s | ||

|power=175 W | |power=175 W | ||

| + | |tdp=375 W | ||

|package name 1=intel,fcbga_3325 | |package name 1=intel,fcbga_3325 | ||

}} | }} | ||

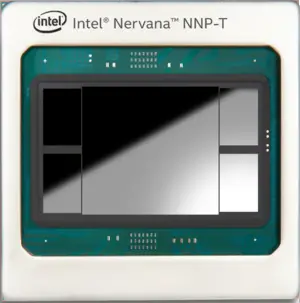

| − | '''NNP-T 1400''' is a [[neural processor]] designed by [[Intel Nervana]] and introduced in late 2019. Fabricated on TSMC [[16 nm process]] based on the {{nervana|Spring Crest|l=arch}} microarchitecture, the NNP-T 1400 has the full 24 {{nervana|Spring Crest#Tensor Processing Cluster (TPC)|TPCs|l=arch}} enabled along with 60 MiB of scratchpad memory and operates at up to 1.1 GHz. This chip comes in an [[OPC OAM|OAM]] [[accelerator card]] form factor and incorporates 32 GiB of [[HBM2]] memory. This NPU exposes 16 {{nervana|Spring Crest#InterChip Link (ICL)|inter-chip links|l=arch}} for scale-out capabilities. | + | '''NNP-T 1400''' is a [[training]] [[neural processor]] designed by [[Intel Nervana]] and introduced in late 2019. Fabricated on TSMC [[16 nm process]] based on the {{nervana|Spring Crest|l=arch}} microarchitecture, the NNP-T 1400 has the full 24 {{nervana|Spring Crest#Tensor Processing Cluster (TPC)|TPCs|l=arch}} enabled along with 60 MiB of scratchpad memory and operates at up to 1.1 GHz. This chip comes in an [[OPC OAM|OAM]] [[accelerator card]] form factor and incorporates 32 GiB of [[HBM2]] memory. This NPU exposes 16 {{nervana|Spring Crest#InterChip Link (ICL)|inter-chip links|l=arch}} for scale-out capabilities. |

[[File:spring crest mezzanine card (front).png|thumb|right|NNP-T 1400 [[OCP OAM|Mezzanine Card]].]] | [[File:spring crest mezzanine card (front).png|thumb|right|NNP-T 1400 [[OCP OAM|Mezzanine Card]].]] | ||

== Peak Performance == | == Peak Performance == | ||

| − | The NNP-T 1400 has a peak performance of [[peak | + | The NNP-T 1400 has a peak performance of [[peak flops (half-precision)::108 TFLOPS]] ([[bfloat16]]). |

== Cache == | == Cache == | ||

Latest revision as of 10:51, 1 February 2020

| Edit Values | |

| NNP-T 1400 | |

| |

| NPU with 4 HBM2 stacks | |

| General Info | |

| Designer | Intel |

| Manufacturer | TSMC |

| Model Number | NNP-T 1400 |

| Market | Server |

| Introduction | November 12, 2019 (announced) November 12, 2019 (launched) |

| Shop | Amazon |

| General Specs | |

| Family | NNP |

| Series | NNP-T |

| Frequency | 1,100 MHz |

| Microarchitecture | |

| Microarchitecture | Spring Crest |

| Process | 16 nm |

| Transistors | 27,000,000,000 |

| Technology | CMOS |

| Die | 680 mm² |

| Cores | 24 |

| Max Memory | 32 GiB |

| Multiprocessing | |

| Interconnect | InterChip Link |

| Interconnect Links | 16 |

| Interconnect Rate | 28 GT/s |

| Electrical | |

| Power dissipation | 175 W |

| TDP | 375 W |

| Packaging | |

| Package | FCBGA-3325 (FCBGA) |

| Dimension | 60 mm × 60 mm |

| Contacts | 3325 |

| |

NNP-T 1400 is a training neural processor designed by Intel Nervana and introduced in late 2019. Fabricated on TSMC 16 nm process based on the Spring Crest microarchitecture, the NNP-T 1400 has the full 24 TPCs enabled along with 60 MiB of scratchpad memory and operates at up to 1.1 GHz. This chip comes in an OAM accelerator card form factor and incorporates 32 GiB of HBM2 memory. This NPU exposes 16 inter-chip links for scale-out capabilities.

NNP-T 1400 Mezzanine Card.

Contents

Peak Performance[edit]

The NNP-T 1400 has a peak performance of 108 TFLOPS108,000,000,000,000 FLOPS

108,000,000,000 KFLOPS

108,000,000 MFLOPS

108,000 GFLOPS

0.108 PFLOPS

(bfloat16).

108,000,000,000 KFLOPS

108,000,000 MFLOPS

108,000 GFLOPS

0.108 PFLOPS

Cache[edit]

- Main article: Spring Crest § Cache

- 60 MiB of tightly-coupled scratchpad memory

- 24 x 2.5 MiB/core

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||

|

||||||||||||

Interconnect Topology[edit]

The NNP-T 1400 comes in an OCP OAM mezzanine card which enables support for various topologies including ring, hybrid cube mesh, and fully connected.

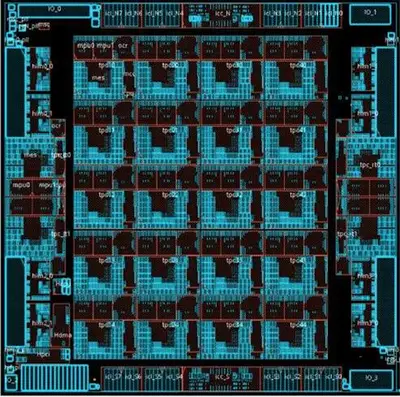

Die[edit]

- Main article: Spring Crest § Die

- 27,000,000,000 transistors

- 680 mm² die size

Product Brief[edit]

Facts about "NNP-T 1400 - Intel Nervana"

| back image |  + + |

| base frequency | 1,100 MHz (1.1 GHz, 1,100,000 kHz) + |

| core count | 24 + |

| designer | Intel + |

| die area | 680 mm² (1.054 in², 6.8 cm², 680,000,000 µm²) + |

| family | NNP + |

| first announced | November 12, 2019 + |

| first launched | November 12, 2019 + |

| full page name | nervana/nnp/nnp-t 1400 + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| ldate | November 12, 2019 + |

| main image |  + + |

| main image caption | NPU with 4 HBM2 stacks + |

| manufacturer | TSMC + |

| market segment | Server + |

| max memory | 32,768 MiB (33,554,432 KiB, 34,359,738,368 B, 32 GiB, 0.0313 TiB) + |

| max memory bandwidth | 1,144.409 GiB/s (1,171,875 MiB/s, 1,228.8 GB/s, 1,228,800 MB/s, 1.118 TiB/s, 1.229 TB/s) + |

| max memory channels | 32 + |

| microarchitecture | Spring Crest + |

| model number | NNP-T 1400 + |

| name | NNP-T 1400 + |

| package | FCBGA-3325 + |

| peak flops (half-precision) | 108,000,000,000,000 FLOPS (108,000,000,000 KFLOPS, 108,000,000 MFLOPS, 108,000 GFLOPS, 108 TFLOPS, 0.108 PFLOPS, 1.08e-4 EFLOPS, 1.08e-7 ZFLOPS) + |

| power dissipation | 175 W (175,000 mW, 0.235 hp, 0.175 kW) + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |

| series | NNP-T + |

| smp interconnect | InterChip Link + |

| smp interconnect links | 16 + |

| smp interconnect rate | 28 GT/s + |

| supported memory type | HBM2-2400 + |

| tdp | 375 W (375,000 mW, 0.503 hp, 0.375 kW) + |

| technology | CMOS + |

| transistor count | 27,000,000,000 + |