From WikiChip

Difference between revisions of "cavium/ccpi"

| (2 intermediate revisions by the same user not shown) | |||

| Line 11: | Line 11: | ||

<tr><th>Lanes/Link</th><td>24</td><td>24</td></tr> | <tr><th>Lanes/Link</th><td>24</td><td>24</td></tr> | ||

<tr><th>Rate/Link</th><td>30 GB/s<br>240 Gb/s</td><td>75 GB/s<br>600 Gb/s</td></tr> | <tr><th>Rate/Link</th><td>30 GB/s<br>240 Gb/s</td><td>75 GB/s<br>600 Gb/s</td></tr> | ||

| − | |||

</table> | </table> | ||

| − | + | == See also == | |

| − | + | * {{cavium|ThunderX}} | |

| − | {{ | + | * {{cavium|ThunderX2}} |

Latest revision as of 00:56, 22 June 2019

| Interconnect Architectures | |

| |

| Concepts | |

| General | |

| Peripheral | |

| Storage Devices | |

| Audio Devices | |

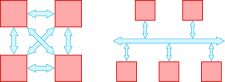

Cavium Coherent Processor Interconnect (CCPI') is an interconnect architecture designed by Cavium for their microprocessors.

Overview[edit]

CCPI is a cache coherent interconnect architecture designed by Cavium for their various microprocessors. CCPI is used to support symmetric multiprocessing on the ThunderX and ThunderX2 families.

Data Rates[edit]

| CCPI | CCPI2 | |

|---|---|---|

| Signaling Rate | 10 GT/s | 25 GT/s |

| Lanes/Link | 24 | 24 |

| Rate/Link | 30 GB/s 240 Gb/s | 75 GB/s 600 Gb/s |