From WikiChip

Difference between revisions of "apm/x-gene/apm883208-x1"

(→Documents) |

|||

| (5 intermediate revisions by 2 users not shown) | |||

| Line 25: | Line 25: | ||

|v io=1.8 V | |v io=1.8 V | ||

|v io 2=2.5 V | |v io 2=2.5 V | ||

| − | |v io | + | |v io 3=3.3 V |

| + | |tdp=45 W | ||

|tjunc min=0 °C | |tjunc min=0 °C | ||

|tjunc max=90 °C | |tjunc max=90 °C | ||

| + | |successor=APM883208-X2 | ||

| + | |successor link=apm/x-gene/apm883208-x2 | ||

}} | }} | ||

'''APM883208-X1''' is a {{arch|64}} [[octa-core]] [[ARM]] server microprocessor designed by [[AppliedMicro]] and introduced in [[2012]]. Fabricated on [[TSMC]] [[40 nm process]] based on the {{apm|Storm|l=arch}} microarchitecture, this processor has eight custom [[ARMv8]] cores operating at up to 2.4 GHz and supporting up to 256 GiB of dual-channel DDR3-1866 memory. | '''APM883208-X1''' is a {{arch|64}} [[octa-core]] [[ARM]] server microprocessor designed by [[AppliedMicro]] and introduced in [[2012]]. Fabricated on [[TSMC]] [[40 nm process]] based on the {{apm|Storm|l=arch}} microarchitecture, this processor has eight custom [[ARMv8]] cores operating at up to 2.4 GHz and supporting up to 256 GiB of dual-channel DDR3-1866 memory. | ||

| Line 50: | Line 53: | ||

== Memory controller == | == Memory controller == | ||

{{memory controller | {{memory controller | ||

| − | |type= | + | |type=DDR3-1866 |

|ecc=Yes | |ecc=Yes | ||

|max mem=256 GiB | |max mem=256 GiB | ||

| Line 98: | Line 101: | ||

* Note: some ports are muxed | * Note: some ports are muxed | ||

| + | |||

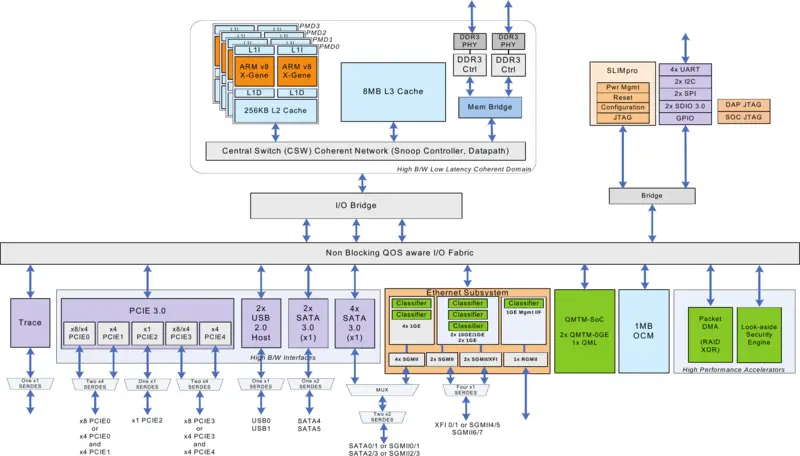

| + | == Block diagram == | ||

| + | :[[File:208-x1-block.png|800px]] | ||

== Documents == | == Documents == | ||

* [[:File:208-X1_PB.pdf|Product Brief]] | * [[:File:208-X1_PB.pdf|Product Brief]] | ||

| − | * [[:File:208-x1-pro-1-x-gene-x-c1-evaluation-kit-product-brief.pdf|APM883208-X1 X-Gene X-C1 Evaluation Kit]] | + | * Eval kits |

| + | ** [[:File:208-x1-pro-1-x-gene-x-c1-evaluation-kit-product-brief.pdf|APM883208-X1 X-Gene X-C1 Evaluation Kit]] | ||

| + | ** [[:File:208-x-gene-x-c1-evaluation-kit-product-brief1.pdf|APM883208-X1 X-Gene X-C1 Evaluation Kit]] | ||

| + | ** [[:File:208-x1-pru-1-x-gene-x-c1-evaluation-kit-product-brief.pdf|APM883208-X1 X-Gene X-C1 Evaluation Kit]] | ||

Latest revision as of 02:10, 26 September 2018

| Edit Values | |

| APM883208-X1 | |

| General Info | |

| Designer | AppliedMicro |

| Manufacturer | TSMC |

| Model Number | APM883208-X1 |

| Market | Server |

| Introduction | October 28, 2011 (announced) 2012 (launched) |

| General Specs | |

| Family | X-Gene |

| Series | X-Gene 1 |

| Turbo Frequency | 2,400 MHz |

| Microarchitecture | |

| ISA | ARMv8 (ARM) |

| Microarchitecture | Storm |

| Core Name | Potenza |

| Process | 40 nm |

| Technology | CMOS |

| Word Size | 64 bit |

| Cores | 8 |

| Threads | 8 |

| Max Memory | 256 GiB |

| Electrical | |

| Vcore | 0.9 V |

| VI/O | 1.8 V, 2.5 V, 3.3 V |

| TDP | 45 W |

| Tjunction | 0 °C – 90 °C |

| Succession | |

APM883208-X1 is a 64-bit octa-core ARM server microprocessor designed by AppliedMicro and introduced in 2012. Fabricated on TSMC 40 nm process based on the Storm microarchitecture, this processor has eight custom ARMv8 cores operating at up to 2.4 GHz and supporting up to 256 GiB of dual-channel DDR3-1866 memory.

Cache[edit]

- Main article: Storm § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions[edit]

Expansion Options |

|||||||||||

|

|||||||||||

- 2x I2C

- 4x UARTs

- GPIOs

- 2x SPI

- 2x SDIO 3.0

- JTAG / Trace

Network[edit]

|

Networking

|

||||||

|

||||||

- Note: some ports are muxed

Block diagram[edit]

Documents[edit]

Facts about "X-Gene 1 APM883208-X1 - AppliedMicro"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | X-Gene 1 APM883208-X1 - AppliedMicro#pcie + |

| core count | 8 + |

| core name | Potenza + |

| core voltage | 0.9 V (9 dV, 90 cV, 900 mV) + |

| designer | AppliedMicro + |

| family | X-Gene + |

| first announced | October 28, 2011 + |

| first launched | 2012 + |

| full page name | apm/x-gene/apm883208-x1 + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| io voltage | 1.8 V (18 dV, 180 cV, 1,800 mV) + and 2.5 V (25 dV, 250 cV, 2,500 mV) + |

| isa | ARMv8 + |

| isa family | ARM + |

| l1$ size | 512 KiB (524,288 B, 0.5 MiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 256 KiB (262,144 B, 0.25 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 256 KiB (262,144 B, 0.25 MiB) + |

| l2$ size | 1 MiB (1,024 KiB, 1,048,576 B, 9.765625e-4 GiB) + |

| l3$ size | 8 MiB (8,192 KiB, 8,388,608 B, 0.00781 GiB) + |

| ldate | 2012 + |

| manufacturer | TSMC + |

| market segment | Server + |

| max junction temperature | 363.15 K (90 °C, 194 °F, 653.67 °R) + |

| max memory | 262,144 MiB (268,435,456 KiB, 274,877,906,944 B, 256 GiB, 0.25 TiB) + |

| max memory bandwidth | 27.82 GiB/s (28,487.68 MiB/s, 29.871 GB/s, 29,871.498 MB/s, 0.0272 TiB/s, 0.0299 TB/s) + |

| max memory channels | 2 + |

| max sata ports | 6 + |

| max usb ports | 2 + |

| microarchitecture | Storm + |

| min junction temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| model number | APM883208-X1 + |

| name | APM883208-X1 + |

| process | 40 nm (0.04 μm, 4.0e-5 mm) + |

| series | X-Gene 1 + |

| supported memory type | DDR4-1866 + |

| technology | CMOS + |

| thread count | 8 + |

| turbo frequency | 2,400 MHz (2.4 GHz, 2,400,000 kHz) + |

| word size | 64 bit (8 octets, 16 nibbles) + |