From WikiChip

Difference between revisions of "Template:interconnect arch"

(fixed) |

|||

| (9 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

| − | < | + | <table class="guidebox"> |

| − | < | + | <tr><td colspan="2">{{Navbar|Template:interconnect_arch|text=|mini=1|style=float:left;}}</td></tr> |

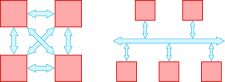

| − | < | + | <tr><td class="header-main" colspan="2">Interconnect<br>Architectures</td></tr> |

| + | <tr><td colspan="2" style="text-align: center;">[[File:interconnect.svg|225px|link=interconnect architecture]]</td></tr> | ||

| + | <tr><td class="header" colspan="2">Concepts</td></tr> | ||

| + | <tr><td colspan="2"> | ||

| + | * [[Network On A Chip]] (NOC) | ||

* [[System Bus]] | * [[System Bus]] | ||

| − | + | </td></tr> | |

| − | < | + | <tr><td class="header" colspan="2">General</td></tr> |

| + | <tr><td colspan="2"> | ||

{{collist | {{collist | ||

| − | | count = | + | | count = 2 |

| | | | ||

| + | * [[CAPI]] | ||

| + | * {{cavium|CCPI}} | ||

| + | * [[ccix|CCIX]] | ||

* [[accelerated graphics port|AGP]] | * [[accelerated graphics port|AGP]] | ||

| − | * [[ | + | * {{ibm|DMI}} ([[IBM]]) |

| + | * {{intel|DMI}} ([[Intel]]) | ||

| + | |||

| + | * {{hisilicon|Hydra}} | ||

| + | * [[hypertransport|HT]] | ||

| + | * [[Gen-Z]] | ||

* [[extended industry standard architecture|EISA]] | * [[extended industry standard architecture|EISA]] | ||

| − | |||

| − | |||

| − | |||

* [[industry standard architecture|ISA]] | * [[industry standard architecture|ISA]] | ||

| + | * {{amd|infinity fabric|IF}} ([[AMD]]) | ||

| + | |||

* [[micro channel|Micro Channel]] | * [[micro channel|Micro Channel]] | ||

* [[Multibus]] | * [[Multibus]] | ||

* {{nvidia|NVLink}} | * {{nvidia|NVLink}} | ||

| − | |||

* [[peripheral component interconnect|PCI]] | * [[peripheral component interconnect|PCI]] | ||

* [[peripheral component interconnect express|PCIe]] | * [[peripheral component interconnect express|PCIe]] | ||

* [[pci extensions for instrumentation|PXI]] | * [[pci extensions for instrumentation|PXI]] | ||

| − | * [[ | + | |

| − | + | * [[Unibus]] | |

* [[S-100]] | * [[S-100]] | ||

* [[SS-50]] | * [[SS-50]] | ||

| − | * [[ | + | * {{tsmc|LIPINCON}} ([[TSMC]]) |

| − | * {{intel|ultrapath interconnect|UPI}} | + | * [[Q-Bus]] |

| + | * {{intel|quickpath interconnect|QPI}} ([[Intel]]) | ||

| + | * {{intel|ultrapath interconnect|UPI}} ([[Intel]]) | ||

* [[vesa local bus|VLB]] | * [[vesa local bus|VLB]] | ||

}} | }} | ||

| − | < | + | </td></tr> |

| − | + | <tr><td class="header" colspan="2">Peripheral</td></tr> | |

| + | <tr><td colspan="2"> | ||

| + | |||

* [[access.bus|ACCESS.bus]] | * [[access.bus|ACCESS.bus]] | ||

| + | * [[UNI/O bus]] | ||

* [[centronics interface|Centronics]] | * [[centronics interface|Centronics]] | ||

* [[general purpose interface bus|GPIB]] | * [[general purpose interface bus|GPIB]] | ||

* [[MIDI]] | * [[MIDI]] | ||

| + | * [[1-wire|1-Wire]] | ||

* [[RS-232]] | * [[RS-232]] | ||

* [[RS-422]] | * [[RS-422]] | ||

* [[RS-423]] | * [[RS-423]] | ||

| − | + | </td></tr> | |

| − | < | + | <tr><td class="header" colspan="2">Storage Devices</td></tr> |

| − | + | <tr><td colspan="2"> | |

* [[parallel ata|PATA]] | * [[parallel ata|PATA]] | ||

* [[serial ata|SATA]] | * [[serial ata|SATA]] | ||

| Line 47: | Line 64: | ||

* [[serial storage architecture|SSA]] | * [[serial storage architecture|SSA]] | ||

* [[small computer system interface|SCSI]] | * [[small computer system interface|SCSI]] | ||

| − | < | + | * [[nvm express|NVMe]] |

| + | </td></tr> | ||

| + | <tr><td class="header" colspan="2">Audio Devices</td></tr> | ||

| + | <tr><td colspan="2"> | ||

* [[inter-ic sound|I²S]] | * [[inter-ic sound|I²S]] | ||

* [[s/pdif|S/PDIF]] | * [[s/pdif|S/PDIF]] | ||

| − | < | + | </td></tr> |

| − | </ | + | </table> |

Latest revision as of 21:29, 17 November 2025

| Interconnect Architectures | |

| |

| Concepts | |

| |

| General | |

| Peripheral | |

| Storage Devices | |

| Audio Devices | |