From WikiChip

Difference between revisions of "intel/cores/tolapai"

| (3 intermediate revisions by the same user not shown) | |||

| Line 2: | Line 2: | ||

{{core | {{core | ||

| name = Tolapai | | name = Tolapai | ||

| − | | image = | + | | image = EP80579 QuickAssist.png |

| caption = | | caption = | ||

| image size = | | image size = | ||

| Line 22: | Line 22: | ||

| socket = BGA-1088 | | socket = BGA-1088 | ||

| − | | succession = | + | | succession = Yes |

| − | | predecessor = | + | | predecessor = Stealey |

| − | | predecessor link = | + | | predecessor link = intel/cores/stealey |

| successor = | | successor = | ||

| successor link = | | successor link = | ||

}} | }} | ||

| − | '''Tolapai''' is the | + | [[File:EP80579.png|right|thumb]] |

| + | '''Tolapai''' is the core for Intel's {{intel|EP80579}} [[system on a chip]]s based on the {{intel|Pentium M|l=arch}} microarchitecture. | ||

== Overview == | == Overview == | ||

| Line 38: | Line 39: | ||

== Members == | == Members == | ||

{{empty section}} | {{empty section}} | ||

| + | |||

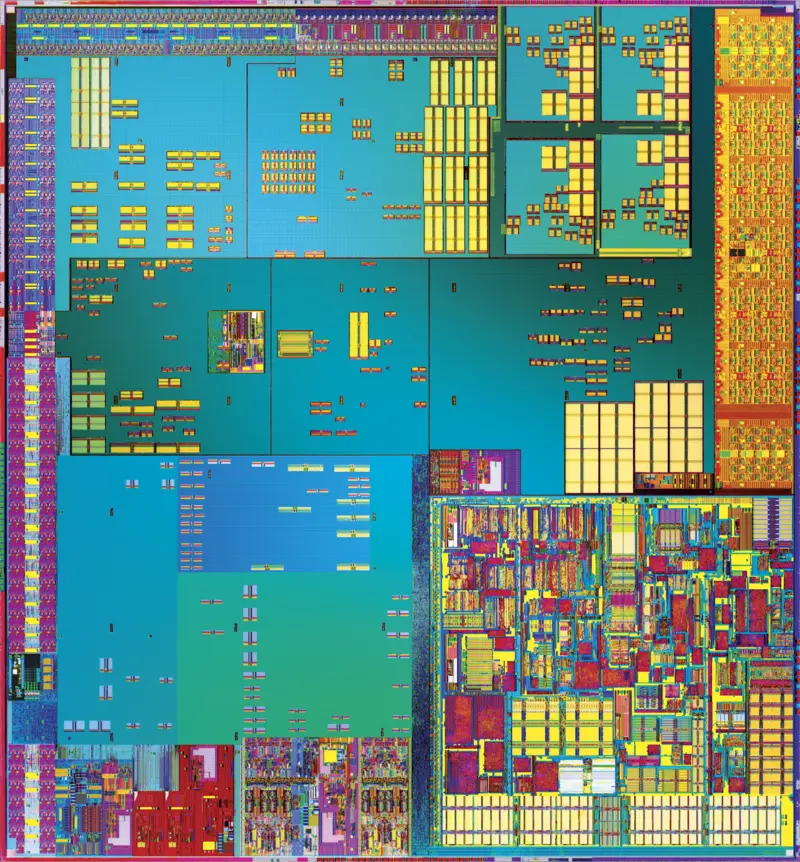

| + | == Die Shot == | ||

| + | * [[90 nm process]] | ||

| + | * 148,000,000 transistors | ||

| + | [[File:Tolapai die shot.png|800px]] | ||

== Documents == | == Documents == | ||

* [[:File:tolapai soc press briefing.pdf|Press Briefing]] | * [[:File:tolapai soc press briefing.pdf|Press Briefing]] | ||

Latest revision as of 04:10, 3 April 2017

| Edit Values | |

| Tolapai | |

| |

| General Info | |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | August 30, 2007 (announced) |

| Microarchitecture | |

| ISA | x86-32 |

| Microarchitecture | Pentium M |

| Word Size | 4 octets 32 bit8 nibbles |

| Process | 90 nm 0.09 μm 9.0e-5 mm |

| Technology | CMOS |

| Clock | 600 MHz - 1,200 MHz |

| Succession | |

Tolapai is the core for Intel's EP80579 system on a chips based on the Pentium M microarchitecture.

Overview[edit]

| This section is empty; you can help add the missing info by editing this page. |

Common Features[edit]

| This section is empty; you can help add the missing info by editing this page. |

Members[edit]

| This section is empty; you can help add the missing info by editing this page. |

Die Shot[edit]

- 90 nm process

- 148,000,000 transistors

Documents[edit]

Facts about "Tolapai - Cores - Intel"

| designer | Intel + |

| first announced | August 30, 2007 + |

| instance of | core + |

| isa | x86-32 + |

| main image |  + + |

| manufacturer | Intel + |

| microarchitecture | Pentium M + |

| name | Tolapai + |

| process | 90 nm (0.09 μm, 9.0e-5 mm) + |

| technology | CMOS + |

| word size | 32 bit (4 octets, 8 nibbles) + |