From WikiChip

Difference between revisions of "ibm/dmi"

(IBM DMI) |

|||

| Line 1: | Line 1: | ||

{{ibm title|Differential Memory Interface (DMI)}}{{interconnect arch}} | {{ibm title|Differential Memory Interface (DMI)}}{{interconnect arch}} | ||

| − | '''Differential Memory Interface''' ('''DMI''') is | + | '''Differential Memory Interface''' ('''DMI''') is an [[IBM]] proprietary memory [[interconnect architecture]] that facilitates serialized, [[memory-agnostic]], communication between a host CPU and a buffered memory chip. |

| + | |||

| + | == Overview == | ||

| + | The Differential Memory Interface is a proprietary interface developed by [[IBM]] designed to transport memory commands, data, and address through a high-speed [[SerDes]] from a host CPU to an OPMB-compliant {{ibm|Centaur|memory buffer chip}}. DMI is a memory-agnostic interface which may be used any sort of memory by abstracting the details behind the buffer chip. DMI was first introduced with {{ibm|POWER8|l=arch}}. | ||

| + | |||

| + | == Implementations == | ||

| + | <table class="wikitable> | ||

| + | <tr><th>Processor</th><td>{{ibm|POWER8|l=arch}}</td><td>{{ibm|POWER9|l=arch}}</td></tr> | ||

| + | <tr><th>Data Rate</th><td>9.6 GT/s</td><td>9.6 GT/s</td></tr> | ||

| + | <tr><th>Links</th><td>4x DMI</td><td>4x DMI</td></tr> | ||

| + | <tr><th>Bandwidth</th><td>28.8 GB/s</td><td>28.8 GB/s</td></tr> | ||

| + | </table> | ||

| + | |||

| + | == See also == | ||

| + | * {{ibm|Centaur}} | ||

| + | * {{ibm|Open Memory Interface}} | ||

Latest revision as of 16:52, 3 November 2019

| Interconnect Architectures | |

| |

| Concepts | |

| General | |

| Peripheral | |

| Storage Devices | |

| Audio Devices | |

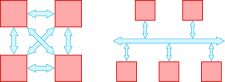

Differential Memory Interface (DMI) is an IBM proprietary memory interconnect architecture that facilitates serialized, memory-agnostic, communication between a host CPU and a buffered memory chip.

Overview[edit]

The Differential Memory Interface is a proprietary interface developed by IBM designed to transport memory commands, data, and address through a high-speed SerDes from a host CPU to an OPMB-compliant memory buffer chip. DMI is a memory-agnostic interface which may be used any sort of memory by abstracting the details behind the buffer chip. DMI was first introduced with POWER8.

Implementations[edit]

| Processor | POWER8 | POWER9 |

|---|---|---|

| Data Rate | 9.6 GT/s | 9.6 GT/s |

| Links | 4x DMI | 4x DMI |

| Bandwidth | 28.8 GB/s | 28.8 GB/s |