m (→History) |

(Fix type) |

||

| (One intermediate revision by one other user not shown) | |||

| Line 35: | Line 35: | ||

== Components == | == Components == | ||

| − | The MCS-4 can be minimally functioning with just the [[/4001|4001]] [[ROM]] and the [[/4004|4004]] [[CPU]], however its designed to be fully functioning with [[RAM]] and [[shift register]]. | + | The MCS-4 can be minimally functioning with just the [[/4001|4001]] [[ROM]] and the [[/4004|4004]] [[CPU]], however its designed to be fully functioning with [[RAM]] and [[shift register]]. Additionally two more chips, the [[/4008|4008]] and [[/4009|4009]], expand the system to work with any of Intel's existing memory chip selections. |

{| class="wikitable" | {| class="wikitable" | ||

| Line 62: | Line 62: | ||

* [[designer::Federico Faggin]] | * [[designer::Federico Faggin]] | ||

* [[designer::Stan Mazor]] | * [[designer::Stan Mazor]] | ||

| − | * [[designer::Masatoshi | + | * [[designer::Masatoshi Shima]] |

| + | |||

== Documents== | == Documents== | ||

* [[:File:MCS-4 Manual.pdf|MCS-4 Manual]] | * [[:File:MCS-4 Manual.pdf|MCS-4 Manual]] | ||

Latest revision as of 21:40, 27 June 2019

| Intel MCS-4 | |

| |

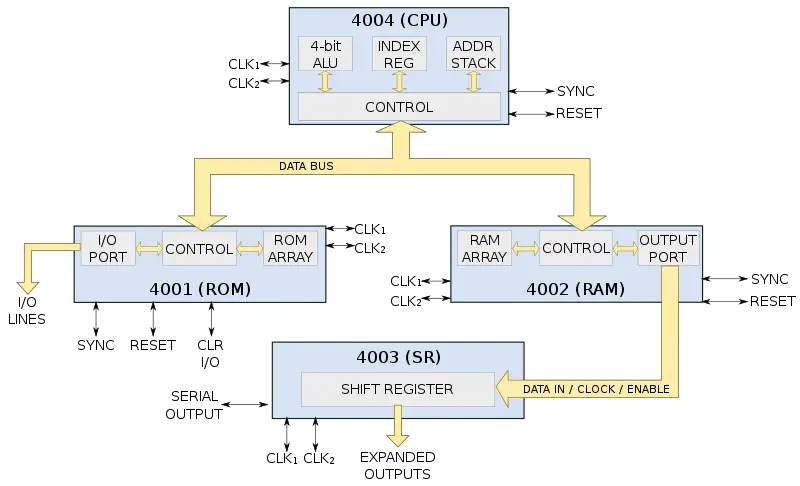

| The entire MCS-4 chipset: 4001, 4002, 4003, and 4004. | |

| Developer | Intel |

| Manufacturer | Intel |

| Type | Microprocessors |

| Production | 1971-1982 |

| Release date | November 15, 1971 |

| Architecture | 4-bit word, 8-bit instruction, BCD-oriented |

| Word size | 4 bit 0.5 octets

1 nibbles |

| Process | 10 μm 10,000 nm

0.01 mm |

| Technology | pMOS |

| Clock | 500 kHz-740 kHz |

| Package | DIP16 |

| Succession | |

| → | |

| MCS-40 | |

The MCS-4 (Micro-Computer Set-4) or 4000 Series or Busicom Chip Set was a family of 4-bit microprocessor chipsets developed by Intel. The entire chipset was made of four individual chips, including the 4004 CPU which became the first commercial microprocessor. MCS-4 was completed by March 1971, entered production in June, and introduced into the market on November 15, 1971.

History[edit]

Before Federico Faggin joined Intel in 1970, the development of the 4004 was rather slow. Federico developed several design innovations at Intel that made it possible to fit the microprocessor in one chip, including new methodology for random logic chip design using silicon gate technology[1]. Faggin developed the 4004 testing tool, chip and logic design concurrently with the layout of all the chips of the entire MCS-4 system.

At the time, Intel was only known for their memory chips. On 15 November 1971, they publicly announced the first commercial microprocessor in the 15th issue of Electronic News. The prophetic ad read: "Announcing a new era in integrated electronics". The chip was designed by Federico Faggin, Ted Hoff and Masatoshi Shima; it received U.S. Patent #3,821,715.

All the MCS-4 components were packaged in 16-pin ceramic DIP. The 16-pin package, which proved to be the most problematic restriction was imposed by management.

Components[edit]

The MCS-4 can be minimally functioning with just the 4001 ROM and the 4004 CPU, however its designed to be fully functioning with RAM and shift register. Additionally two more chips, the 4008 and 4009, expand the system to work with any of Intel's existing memory chip selections.

| Part | Description |

|---|---|

| 4001 | ROM |

| 4002 | RAM |

| 4003 | shift register |

| 4004 | MPU |

| 4008 | Address latch |

| 4009 | I/O Interface |

Architecture[edit]

| This section is empty; you can help add the missing info by editing this page. |

Lead Designers[edit]

Lead designers for the MCS-4 family were:

- Ted Hoff

- Federico Faggin

- Stan Mazor

- Masatoshi Shima

Documents[edit]

References[edit]

- ↑ Faggin. Il padre del chip intelligente, Angelo Gallippi, 2002, 88-7118-149-2

See Also[edit]

| This article is still a stub and needs your attention. You can help improve this article by editing this page and adding the missing information. |

| designer | Intel +, Ted Hoff +, Federico Faggin +, Stan Mazor + and Masatoshi Shima + |

| full page name | intel/mcs-4 + |

| instance of | microprocessor family + |

| main designer | Intel + |

| manufacturer | Intel + |

| name | Intel MCS-4 + |

| package | DIP16 + |

| process | 10,000 nm (10 μm, 0.01 mm) + |

| technology | pMOS + |

| word size | 4 bit (0.5 octets, 1 nibbles) + |