| (18 intermediate revisions by 8 users not shown) | |||

| Line 1: | Line 1: | ||

| − | {{mediatek title|Helio X30}} | + | {{mediatek title|Helio X30 (MT6799)}} |

| − | {{ | + | {{chip |

| − | + | |name=MediaTek Helio X30 | |

| − | | name | + | |no image=Yes |

| − | | no image | + | |designer=MediaTek |

| − | + | |designer 2=ARM Holdings | |

| − | + | |manufacturer=TSMC | |

| − | + | |model number=Helio X30 | |

| − | | designer | + | |part number=MT6799 |

| − | | designer 2 | + | |market=Mobile |

| − | | manufacturer | + | |market 2=Embedded |

| − | | model number | + | |first announced=September 26, 2016 |

| − | | part number | + | |first launched=February 27, 2017 |

| − | + | |family=Helio | |

| − | | market | + | |series=Helio X |

| − | | market 2 | + | |frequency=2,500 MHz |

| − | | first announced | + | |frequency 2=2,200 MHz |

| − | | first launched | + | |frequency 3=1,900 MHz |

| − | | | + | |bus type=AMBA 4 AXI |

| − | | | + | |isa=ARMv8 |

| − | | | + | |isa family=ARM |

| + | |microarch=Cortex-A53 | ||

| + | |microarch 2=Cortex-A73 | ||

| + | |microarch 3=Cortex-A35 | ||

| + | |core name=Cortex-A35 | ||

| + | |core name 2=Cortex-A53 | ||

| + | |core name 3=Cortex-A73 | ||

| + | |process=10 nm | ||

| + | |technology=CMOS | ||

| + | |word size=64 bit | ||

| + | |core count=10 | ||

| + | |thread count=10 | ||

| + | |max cpus=1 | ||

| + | |max memory=8 GiB | ||

| + | }} | ||

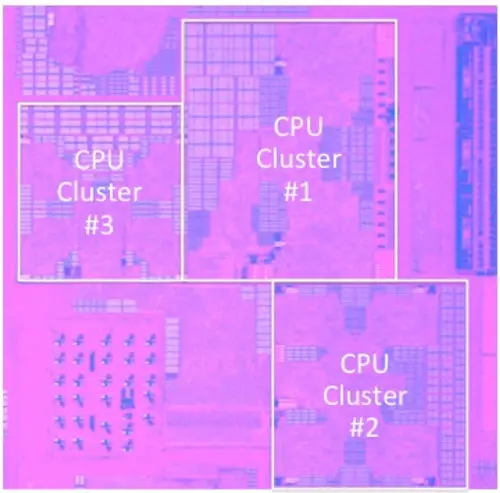

| + | '''Helio X30''' ('''MT6799''') is a {{arch|64}} [[deca-core]] [[ARM]] [[LTE]] system on a chip designed by [[MediaTek]] and launched in early [[2017]]. This SoC incorporates 3 independent clusters of cores (called "Tri-Cluster" by MediaTek) operating at varying degrees of performance designed for certain workloads (operating at 1.9 GHz, 2.2 GHz, and 2.5 GHz) and supports up to 8 GiB of quad-channel LPDDR4X-3732 memory. This SoC also incorporates a {{imgtec|PowerVR GT7400 Plus}} [[IGP]] operating at 800 MHz. The chip has a modem supporting [[LTE]] User Equipment (UE) category 10. | ||

| + | |||

| + | == Architecture == | ||

| + | The Helio X30 is designed is composed of 3 individual clusters of CPU cores depending on the level of performance required by the active applications. | ||

| + | |||

| + | * Extreme Performance - 2x {{armh|Cortex-A73|l=arch}} @ 2.5 GHz | ||

| + | * Performance/Power Balance - 4x {{armh|Cortex-A53|l=arch}} @ 2.2 GHz | ||

| + | * Power Efficiency - 4x {{armh|Cortex-A35|l=arch}} @ 1.9 GHz | ||

| + | |||

| + | The three clusters are designed as a modified {{armh|big.LITTLE}} configuration. | ||

| + | |||

| + | == Cache == | ||

| + | {{main|arm holdings/microarchitectures/cortex-a53#Memory_Hierarchy|arm holdings/microarchitectures/cortex-a73#Memory_Hierarchy|l1=Cortex-A53 § Cache|l2=Cortex-A73 § Cache}} | ||

| + | {{empty section}} | ||

| − | + | == Memory controller == | |

| − | | | + | {{memory controller |

| − | | | + | |type=LPDDR4X-3732 |

| − | | | + | |ecc=No |

| − | | | + | |max mem=8 GiB |

| − | | | + | |controllers=1 |

| − | | | + | |channels=4 |

| − | | | + | |width=16 bit |

| − | | | + | |max bandwidth=27.81 GiB/s |

| − | | | + | |bandwidth schan=6.95 GiB/s |

| − | | | + | |bandwidth dchan=13.9 GiB/s |

| + | |bandwidth qchan=27.81 GiB/s | ||

| + | }} | ||

| − | + | == Expansions == | |

| − | + | {{expansions | |

| − | + | |usb revision=2.0 | |

| − | + | |usb revision 2=3.0 | |

| − | | | + | |usb ports=8 |

| − | | | + | |uart=4 |

| − | | | + | |gp io=Yes |

| − | | | + | }} |

| − | | | + | |

| − | + | == Graphics == | |

| − | + | {{integrated graphics | |

| − | + | | gpu = PowerVR GT7400 Plus | |

| − | + | | device id = | |

| − | + | | designer = Imagination Technologies | |

| − | + | | execution units = | |

| − | + | | max displays = | |

| − | | | ||

| − | | | ||

| − | | | ||

| − | | | ||

| − | | max | ||

| max memory = | | max memory = | ||

| + | | frequency = 800 MHz | ||

| − | | | + | | output dsi = Yes |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | | | + | | max res dsi = 3840x2160 |

| − | | | + | |

| − | | | + | | direct3d ver = 11.2 |

| − | + | | opencl ver = 2.0 | |

| − | | | + | | opengl ver = 3.3 |

| − | | | + | | opengl es ver = 3.2 |

| − | | | + | | vulkan ver = 1.0 |

| − | |||

}} | }} | ||

| − | + | ||

| + | == Wireless == | ||

| + | {{wireless links | ||

| + | | wifi = Yes | ||

| + | | 80211ac = Yes | ||

| + | |||

| + | | 2g = Yes | ||

| + | | csd = Yes | ||

| + | | gsm = Yes | ||

| + | | gprs = Yes | ||

| + | | edge = Yes | ||

| + | | cdmaone = | ||

| + | | is-95a = | ||

| + | | is-95b = | ||

| + | | 3g = Yes | ||

| + | | cdma2000 = Yes | ||

| + | | cdma2000 1x = Yes | ||

| + | | cdma2000 1xev-do = Yes | ||

| + | | cdma2000 1x adv = | ||

| + | | umts = Yes | ||

| + | | wcdma = | ||

| + | | td-scdma = Yes | ||

| + | | dc-hsdpa = Yes | ||

| + | | hsdpa = | ||

| + | | hsupa = Yes | ||

| + | | 4g = Yes | ||

| + | | lte a = Yes | ||

| + | | e-utran = Yes | ||

| + | | ue cat = 10 | ||

| + | }} | ||

| + | |||

| + | == Image == | ||

| + | * Integrated image signal processor supports 28 MP | ||

| + | * Supports image stabilization | ||

| + | * Supports video stabilization | ||

| + | * Supports noise reduction | ||

| + | * Supports lens shading correction | ||

| + | * Supports AE/AWB/AF | ||

| + | * Supports edge enhancement | ||

| + | * Supports face detection and visual tracking | ||

| + | * Hardware JPEG encoder | ||

| + | |||

| + | == Video == | ||

| + | * Video encoding 4K2K @ 30fps with H.265 and HDR | ||

| + | * Video decoding 4K2K @ 30fps, h.264, h.265 / HEVC, MPEG-1/2/4, VC-1, VP-8, VP-9 | ||

| + | |||

| + | == Audio == | ||

| + | * Audio content sampling rates 8kHz to 192kHz | ||

| + | * Audio content sampling format 8-bit/16-bit/24-bit Mono/Stereo | ||

| + | * I2S, PCM | ||

| + | * Encode: AMR-NB, AMR-WB, AAC, OGG, ADPCM | ||

| + | * Decode: WAV, MP3, MP2, AAC, AMR-NB, AMR-WB, MIDI, Vorbis, APE, AAC-plus v1, AAC-plus v2, FLAC, WMA, ADPCM | ||

| + | * 7.1 channel MHL output | ||

| + | |||

| + | == Utilizing devices == | ||

| + | * [[used by::Meizu Pro 7]] | ||

| + | * [[used by::Meizu Pro 7 Plus]] | ||

| + | {{expand list}} | ||

| + | |||

| + | == Die == | ||

| + | * [[10 nm process]] | ||

| + | |||

| + | :[[File:x30 die shot.png|500px]] | ||

| + | |||

| + | == Bibliography == | ||

| + | * Mair, Hugh, et al. "3.4 A 10nm FinFET 2.8 GHz tri-gear deca-core CPU complex with optimized power-delivery network for mobile SoC performance." Solid-State Circuits Conference (ISSCC), 2017 IEEE International. IEEE, 2017. | ||

Latest revision as of 15:22, 29 December 2018

| Edit Values | |

| MediaTek Helio X30 | |

| General Info | |

| Designer | MediaTek, ARM Holdings |

| Manufacturer | TSMC |

| Model Number | Helio X30 |

| Part Number | MT6799 |

| Market | Mobile, Embedded |

| Introduction | September 26, 2016 (announced) February 27, 2017 (launched) |

| General Specs | |

| Family | Helio |

| Series | Helio X |

| Frequency | 2,500 MHz, 2,200 MHz, 1,900 MHz |

| Bus type | AMBA 4 AXI |

| Microarchitecture | |

| ISA | ARMv8 (ARM) |

| Microarchitecture | Cortex-A53, Cortex-A73, Cortex-A35 |

| Core Name | Cortex-A35, Cortex-A53, Cortex-A73 |

| Process | 10 nm |

| Technology | CMOS |

| Word Size | 64 bit |

| Cores | 10 |

| Threads | 10 |

| Max Memory | 8 GiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

Helio X30 (MT6799) is a 64-bit deca-core ARM LTE system on a chip designed by MediaTek and launched in early 2017. This SoC incorporates 3 independent clusters of cores (called "Tri-Cluster" by MediaTek) operating at varying degrees of performance designed for certain workloads (operating at 1.9 GHz, 2.2 GHz, and 2.5 GHz) and supports up to 8 GiB of quad-channel LPDDR4X-3732 memory. This SoC also incorporates a PowerVR GT7400 Plus IGP operating at 800 MHz. The chip has a modem supporting LTE User Equipment (UE) category 10.

Contents

Architecture[edit]

The Helio X30 is designed is composed of 3 individual clusters of CPU cores depending on the level of performance required by the active applications.

- Extreme Performance - 2x Cortex-A73 @ 2.5 GHz

- Performance/Power Balance - 4x Cortex-A53 @ 2.2 GHz

- Power Efficiency - 4x Cortex-A35 @ 1.9 GHz

The three clusters are designed as a modified big.LITTLE configuration.

Cache[edit]

- Main articles: Cortex-A53 § Cache and Cortex-A73 § Cache

| This section is empty; you can help add the missing info by editing this page. |

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Expansions[edit]

|

Expansion Options

|

||||||||||

|

||||||||||

Graphics[edit]

|

Integrated Graphics Information

|

||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||

Wireless[edit]

| Wi-Fi | ||||||||||||||||

| WiFi |

| |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Cellular | ||||||||||||||||

| 2G |

| |||||||||||||||

| 3G |

| |||||||||||||||

| 4G |

| |||||||||||||||

Image[edit]

- Integrated image signal processor supports 28 MP

- Supports image stabilization

- Supports video stabilization

- Supports noise reduction

- Supports lens shading correction

- Supports AE/AWB/AF

- Supports edge enhancement

- Supports face detection and visual tracking

- Hardware JPEG encoder

Video[edit]

- Video encoding 4K2K @ 30fps with H.265 and HDR

- Video decoding 4K2K @ 30fps, h.264, h.265 / HEVC, MPEG-1/2/4, VC-1, VP-8, VP-9

Audio[edit]

- Audio content sampling rates 8kHz to 192kHz

- Audio content sampling format 8-bit/16-bit/24-bit Mono/Stereo

- I2S, PCM

- Encode: AMR-NB, AMR-WB, AAC, OGG, ADPCM

- Decode: WAV, MP3, MP2, AAC, AMR-NB, AMR-WB, MIDI, Vorbis, APE, AAC-plus v1, AAC-plus v2, FLAC, WMA, ADPCM

- 7.1 channel MHL output

Utilizing devices[edit]

- Meizu Pro 7

- Meizu Pro 7 Plus

This list is incomplete; you can help by expanding it.

Die[edit]

Bibliography[edit]

- Mair, Hugh, et al. "3.4 A 10nm FinFET 2.8 GHz tri-gear deca-core CPU complex with optimized power-delivery network for mobile SoC performance." Solid-State Circuits Conference (ISSCC), 2017 IEEE International. IEEE, 2017.

- all microprocessor models

- microprocessor models by mediatek

- microprocessor models by mediatek based on cortex-a53

- microprocessor models by mediatek based on cortex-a73

- microprocessor models by mediatek based on cortex-a35

- microprocessor models by arm holdings

- microprocessor models by arm holdings based on cortex-a53

- microprocessor models by arm holdings based on cortex-a73

- microprocessor models by arm holdings based on cortex-a35

- microprocessor models by tsmc