-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

Difference between revisions of "mediatek/mt65xx/mt6595"

< mediatek

(MT6595) |

(No difference)

|

Revision as of 08:02, 29 December 2018

| Edit Values | |

| |

| General Info | |

| Microarchitecture |

MT6595 is a mid-range octa-core ARM LTE SoC designed by MediaTek and introduced in early 2014. This chip, which is fabricated on TSMC's 28 nm process, features four big Cortex-A17 cores operating at up to 2.5 GHz and four little Cortex-A7 cores operating at up to 1.7 GHz. The MT6595 incorporates an PowerVR G6200 GPU operating at up to 600 MHz and supports up to dual-channel LPDDR3-1866 memory.

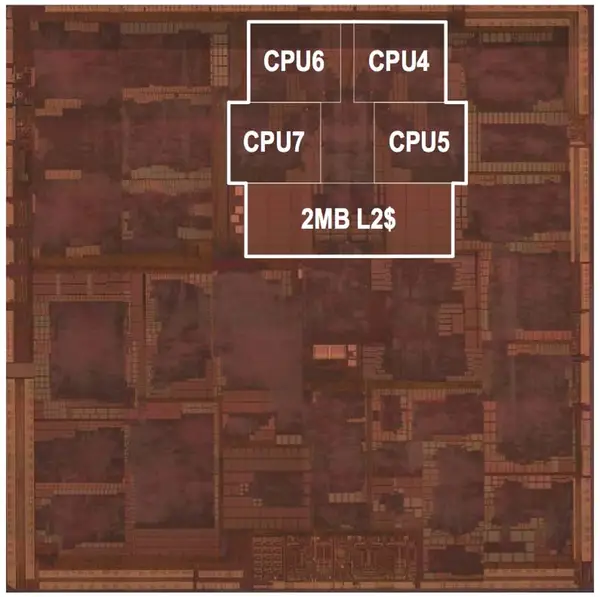

Die

- TSMC 28 nm process

- 89 mm² die size

- Quad-core Cortex-A7

- ~0.48 mm² per core

- Quad-core Cortex-A17 + 2 MiB L2

- ~1.93 mm² per core

- ~3.93 mm² for 2 MiB L2

(small quad-core is unlabeled below the big core cluster)

Facts about "MT6595 - MediaTek"

| full page name | mediatek/mt65xx/mt6595 + |

| instance of | microprocessor + |

| ldate | 1900 + |