From WikiChip

Difference between revisions of "bitmain/sophon/bm1880"

(BM1880) |

|||

| (2 intermediate revisions by the same user not shown) | |||

| Line 11: | Line 11: | ||

|first launched=October 17, 2018 | |first launched=October 17, 2018 | ||

|family=Sophon | |family=Sophon | ||

| + | |isa=RV32I | ||

| + | |isa family=RISC-V | ||

| + | |isa 2=ARMv8 | ||

| + | |isa 2 family=ARM | ||

| + | |microarch=Cortex-A53 | ||

| + | |microarch 2=RISC-V | ||

| + | |core name=Cortex-A53 | ||

| + | |core name 2=RISC-V | ||

|technology=CMOS | |technology=CMOS | ||

| + | |max memory=4 GiB | ||

| + | |v core=0.9 V | ||

| + | |v io=1.8 V | ||

| + | |v io 2=3.3 V | ||

| + | |tdp typical=2.5 W | ||

}} | }} | ||

'''Sophon BM1880''' is a [[neural processor]] designed by [[Bitmain]] launched in [[2018]] for edge applications. This chip is designed primarily for edge inference acceleration and has a peak performance of [[peak integer ops (8-bit)::2 TOPS]] (INT8) and a typical power consumption of 2.5 W. | '''Sophon BM1880''' is a [[neural processor]] designed by [[Bitmain]] launched in [[2018]] for edge applications. This chip is designed primarily for edge inference acceleration and has a peak performance of [[peak integer ops (8-bit)::2 TOPS]] (INT8) and a typical power consumption of 2.5 W. | ||

| + | |||

| + | == Overview == | ||

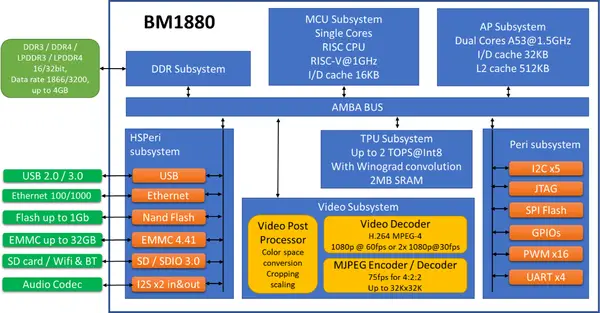

| + | The BM1880 is a [[neural processor]] designed for edge inference at low power consumption. The chip integrates a single-core [[RISC-V]] MCU subsystem operating at 1 GHz along with a dual-core {{armh|Cortex-A53|l=arch}} application processor operating at 1.5 GHz along with a TPU subsystem by BitMain capable of up to 2 teraOPS (8-bit integer). The chip also includes a capable video subsystem for video and image processing from a camera directly on-chip. | ||

| + | |||

| + | |||

| + | :[[File:bm1880 block diagram.png|thumb|left|600px|Block Diagram]] | ||

| + | {{clear}} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR4-3200 | ||

| + | |ecc=No | ||

| + | |max mem=4 GiB | ||

| + | |controllers=1 | ||

| + | |channels=2 | ||

| + | |width=32 bit | ||

| + | |max bandwidth=11.92 GiB/s | ||

| + | |bandwidth schan=11.92 GiB/s | ||

| + | }} | ||

| + | |||

| + | == Video Subsystem == | ||

| + | * H.264 Video decoder | ||

| + | * MJPEG encoder/decoder | ||

| + | * Video Post Processor | ||

| + | * 1080P@60fps or 2 channel 1080p@30fps | ||

| + | |||

| + | == Expansions == | ||

| + | * One USB 3.0/USB2.0 host/device | ||

| + | * Two Integrated GMAC for RGMII/RMII | ||

| + | * 5xI2C / 16x PWM / 4x UART / Multi GPIO | ||

| + | |||

| + | == Documents == | ||

| + | * [[:File:BM1880 PB V0.07.pdf|Product Brief]] | ||

Latest revision as of 12:19, 25 December 2018

| Edit Values | |

| Sophon BM1880 | |

| General Info | |

| Designer | Bitmain |

| Manufacturer | TSMC |

| Model Number | BM1880 |

| Market | Edge Compute |

| Introduction | October 17, 2018 (announced) October 17, 2018 (launched) |

| General Specs | |

| Family | Sophon |

| Microarchitecture | |

| ISA | RV32I (RISC-V), ARMv8 (ARM) |

| Microarchitecture | Cortex-A53, RISC-V |

| Core Name | Cortex-A53, RISC-V |

| Technology | CMOS |

| Max Memory | 4 GiB |

| Electrical | |

| Vcore | 0.9 V |

| VI/O | 1.8 V, 3.3 V |

| TDP (Typical) | 2.5 W |

2,000,000,000,000 OPS

2,000,000,000 KOPS

2,000,000 MOPS

2,000 GOPS

0.002 POPS

(INT8) and a typical power consumption of 2.5 W.

2,000,000,000 KOPS

2,000,000 MOPS

2,000 GOPS

0.002 POPS

Overview[edit]

The BM1880 is a neural processor designed for edge inference at low power consumption. The chip integrates a single-core RISC-V MCU subsystem operating at 1 GHz along with a dual-core Cortex-A53 application processor operating at 1.5 GHz along with a TPU subsystem by BitMain capable of up to 2 teraOPS (8-bit integer). The chip also includes a capable video subsystem for video and image processing from a camera directly on-chip.

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Video Subsystem[edit]

- H.264 Video decoder

- MJPEG encoder/decoder

- Video Post Processor

- 1080P@60fps or 2 channel 1080p@30fps

Expansions[edit]

- One USB 3.0/USB2.0 host/device

- Two Integrated GMAC for RGMII/RMII

- 5xI2C / 16x PWM / 4x UART / Multi GPIO

Documents[edit]

Facts about "Sophon BM1880 - Bitmain"

| core name | Cortex-A53 + and RISC-V + |

| core voltage | 0.9 V (9 dV, 90 cV, 900 mV) + |

| designer | Bitmain + |

| family | Sophon + |

| first announced | October 17, 2018 + |

| first launched | October 17, 2018 + |

| full page name | bitmain/sophon/bm1880 + |

| has ecc memory support | false + |

| instance of | microprocessor + |

| io voltage | 1.8 V (18 dV, 180 cV, 1,800 mV) + and 3.3 V (33 dV, 330 cV, 3,300 mV) + |

| isa | RV32I + and ARMv8 + |

| isa family | RISC-V + and ARM + |

| ldate | 3000 + |

| manufacturer | TSMC + |

| market segment | Edge Compute + |

| max memory | 4,096 MiB (4,194,304 KiB, 4,294,967,296 B, 4 GiB, 0.00391 TiB) + |

| max memory bandwidth | 11.92 GiB/s (12,206.08 MiB/s, 12.799 GB/s, 12,799.003 MB/s, 0.0116 TiB/s, 0.0128 TB/s) + |

| max memory channels | 2 + |

| microarchitecture | Cortex-A53 + and RISC-V + |

| model number | BM1880 + |

| name | Sophon BM1880 + |

| peak integer ops (8-bit) | 2,000,000,000,000 OPS (2,000,000,000 KOPS, 2,000,000 MOPS, 2,000 GOPS, 2 TOPS, 0.002 POPS, 2.0e-6 EOPS, 2.0e-9 ZOPS) + |

| supported memory type | DDR4-3200 + |

| tdp (typical) | 2.5 W (2,500 mW, 0.00335 hp, 0.0025 kW) + |

| technology | CMOS + |