From WikiChip

Difference between revisions of "intel/atom x5/x5-e3940"

m (Bot: moving all {{mpu}} to {{chip}}) |

|||

| (18 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

{{intel title|Atom x5-E3940}} | {{intel title|Atom x5-E3940}} | ||

| − | {{ | + | {{chip |

| name = Intel Atom x5-E3940 | | name = Intel Atom x5-E3940 | ||

| − | | no image = | + | | no image = |

| − | | image = | + | | image = Atom E3900 SoC Front.png |

| image size = | | image size = | ||

| caption = | | caption = | ||

| + | | designer = Intel | ||

| manufacturer = Intel | | manufacturer = Intel | ||

| model number = x5-E3940 | | model number = x5-E3940 | ||

| part number = | | part number = | ||

| − | | market = | + | | market = Embedded |

| first announced = October 26, 2016 | | first announced = October 26, 2016 | ||

| first launched = 2017 | | first launched = 2017 | ||

| Line 39: | Line 40: | ||

| die size = | | die size = | ||

| word size = 64 bit | | word size = 64 bit | ||

| − | | core count = | + | | core count = 4 |

| − | | thread count = | + | | thread count = 4 |

| max cpus = 1 | | max cpus = 1 | ||

| − | | max memory = | + | | max memory = 8 GiB |

| max memory addr = | | max memory addr = | ||

| − | + | ||

| power = | | power = | ||

| − | | sdp = | + | | sdp = |

| − | | tdp = | + | | tdp = 9.5 W |

| ctdp down = | | ctdp down = | ||

| ctdp down frequency = | | ctdp down frequency = | ||

| Line 70: | Line 71: | ||

| socket 0 type = BGA | | socket 0 type = BGA | ||

}} | }} | ||

| − | The '''Atom x5-E3940''' is a {{arch|64}} dual-core | + | The '''Atom x5-E3940''' is a {{arch|64}} [[dual-core]] [[x86]] system on a chip set to be introduced by [[Intel]] in early 2017. This ultra-low power MPU, which was specifically designed for the [[internet of things|IoTs]], operates at 1.6 GHz and has a TDP of 9.5 W. This chip is based on the {{intel|Goldmont|l=arch}}, manufactured on Intel's enhanced [[14 nm process]]. |

| − | |||

| − | |||

== Cache == | == Cache == | ||

{{main|intel/microarchitectures/goldmont#Memory_Hierarchy|l1=Goldmont § Cache}} | {{main|intel/microarchitectures/goldmont#Memory_Hierarchy|l1=Goldmont § Cache}} | ||

| Line 95: | Line 94: | ||

== Memory controller == | == Memory controller == | ||

{{integrated memory controller | {{integrated memory controller | ||

| − | | type = | + | | type = DDR3L-1866 |

| − | | type 2 | + | | type 2 = LPDDR4-2133 |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| controllers = 1 | | controllers = 1 | ||

| − | | channels = | + | | channels = 4 |

| ecc support = Yes | | ecc support = Yes | ||

| − | | bandwidth schan = | + | | max bandwidth = 31.79 GiB/s |

| − | | bandwidth dchan = | + | | bandwidth schan = 15.89 GiB/s |

| − | | max memory = 8 | + | | bandwidth dchan = 31.79 GiB/s |

| + | | max memory = 8 GiB | ||

| + | | pae = 40 bit | ||

}} | }} | ||

| Line 118: | Line 112: | ||

| execution units = 12 | | execution units = 12 | ||

| displays = 3 | | displays = 3 | ||

| − | | frequency = | + | | frequency = 400 MHz |

| − | | max frequency = | + | | max frequency = 600 MHz |

| − | | max memory = | + | | max memory = 2 GiB |

| output crt = | | output crt = | ||

| Line 155: | Line 149: | ||

| max res vga freq = | | max res vga freq = | ||

| − | | intel quick sync = | + | | intel quick sync = Yes |

| intel intru 3d = | | intel intru 3d = | ||

| intel insider = | | intel insider = | ||

| intel widi = | | intel widi = | ||

| intel fdi = | | intel fdi = | ||

| − | | intel clear video = | + | | intel clear video = Yes |

}} | }} | ||

| Line 167: | Line 161: | ||

== Expansions == | == Expansions == | ||

| − | {{ | + | {{expansions |

| pcie revision = 2.0 | | pcie revision = 2.0 | ||

| pcie lanes = 4 | | pcie lanes = 4 | ||

| Line 184: | Line 178: | ||

== Features == | == Features == | ||

| − | {{ | + | {{x86 features |

| em64t = Yes | | em64t = Yes | ||

| nx = Yes | | nx = Yes | ||

| − | | txt = | + | | txt = |

| tsx = | | tsx = | ||

| vpro = | | vpro = | ||

| Line 219: | Line 213: | ||

| os guard = | | os guard = | ||

| intel at = | | intel at = | ||

| + | | intel ipt = Yes | ||

}} | }} | ||

| + | |||

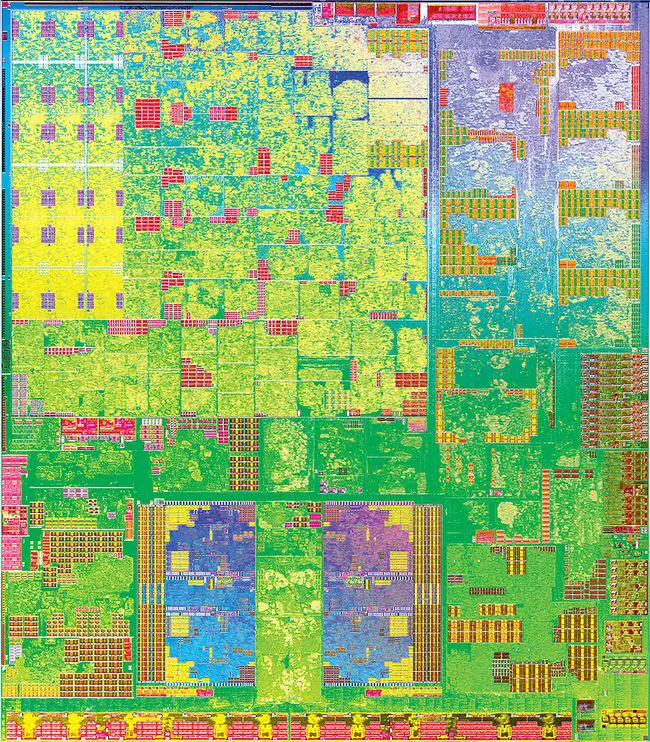

| + | == Die Shot == | ||

| + | Intel {{intel|Goldmont|l=arch}}-based {{intel|Atom}} E3900 SoC series die shot: | ||

| + | :[[File:atom e3900 die shot.jpg|650px]] | ||

| + | |||

| + | == Documents == | ||

| + | * [[:File:atom-e3900-fact-sheet.pdf|Intel Atom Processor E3900 Series Fact Sheet]] | ||

Latest revision as of 16:15, 13 December 2017

| Edit Values | |

| Intel Atom x5-E3940 | |

| |

| General Info | |

| Designer | Intel |

| Manufacturer | Intel |

| Model Number | x5-E3940 |

| Market | Embedded |

| Introduction | October 26, 2016 (announced) 2017 (launched) |

| Shop | Amazon |

| General Specs | |

| Family | Atom x5 |

| Series | E3900 |

| Locked | Yes |

| Frequency | 1600 MHz |

| Turbo Frequency | Yes |

| Turbo Frequency | 1800 MHz (1 core) |

| Microarchitecture | |

| Microarchitecture | Goldmont |

| Platform | Apollo Lake |

| Core Name | Apollo Lake |

| Process | 14 nm |

| Technology | CMOS |

| Word Size | 64 bit |

| Cores | 4 |

| Threads | 4 |

| Max Memory | 8 GiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| TDP | 9.5 W |

| Tjunction | -40 °C – 110 °C |

The Atom x5-E3940 is a 64-bit dual-core x86 system on a chip set to be introduced by Intel in early 2017. This ultra-low power MPU, which was specifically designed for the IoTs, operates at 1.6 GHz and has a TDP of 9.5 W. This chip is based on the Goldmont, manufactured on Intel's enhanced 14 nm process.

Cache[edit]

- Main article: Goldmont § Cache

| Cache Info [Edit Values] | ||

| L1I$ | 64 KiB 65,536 B 0.0625 MiB |

2x32 KiB 8-way set associative (per core) |

| L1D$ | 48 KiB 49,152 B 0.0469 MiB |

2x24 KiB 6-way set associative (per core) |

| L2$ | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB |

2x1 MiB 16-way set associative (per 2 cores) |

| L3$ | 0 KiB 0 MiB 0 B 0 GiB |

No L3$ |

Memory controller[edit]

| Integrated Memory Controller | |

| Type | DDR3L-1866, LPDDR4-2133 |

| Controllers | 1 |

| Channels | 4 |

| ECC Support | Yes |

| Max bandwidth | 31.79 GiB/s |

| Bandwidth (single) | 15.89 GiB/s |

| Bandwidth (dual) | 31.79 GiB/s |

| Max memory | 8 GiB |

| Physical Address Extensions | 40 bit |

Graphics[edit]

| Integrated Graphic Information | |

| GPU | HD Graphics 500 |

| Device ID | 0x5A85 |

| Execution Units | 12 |

| Displays | 3 |

| Frequency | 400 MHz 0.4 GHz

400,000 KHz |

| Max frequency | 600 MHz 0.6 GHz

600,000 KHz |

| Max memory | 2 GiB 2,048 MiB

2,097,152 KiB 2,147,483,648 B |

| Output | DisplayPort, Embedded DisplayPort, HDMI, DSI |

| DirectX | 12 |

| OpenGL | 4.3 |

| OpenCL | 1.2 |

| OpenGL ES | 3.0 |

| HDMI | 1.4b |

| DP | 1.2 |

| eDP | 1.3 |

| Max HDMI Res | 3840x2160 @30 Hz |

| Max DSI Res | 2560x1600 @60 Hz |

| Max DP Res | 4096x2160 @60 Hz |

| Max eDP Res | 3840x2160 @60 Hz |

| Intel Quick Sync Video | |

| Intel Clear Video | |

- Video decode hardware acceleration including support for HEVC (H.265), H.264, MVC, VP8, VP9, MPEG2, VC-1, WMV9, JPEG/MJPEG.

- Video encode hardware acceleration including support for HEVC (H.265), H.264, MVC, VP8, VP9, JPEG/MJPEG.

Expansions[edit]

|

Expansion Options

|

||||||||||||||||||||||

|

||||||||||||||||||||||

Features[edit]

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||

|

||||||||||||||||||||

Die Shot[edit]

Intel Goldmont-based Atom E3900 SoC series die shot:

Documents[edit]

Facts about "Atom x5-E3940 - Intel"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Atom x5-E3940 - Intel#io + |

| base frequency | 1,600 MHz (1.6 GHz, 1,600,000 kHz) + |

| core count | 4 + |

| core name | Apollo Lake + |

| designer | Intel + |

| device id | 0x5A85 + |

| family | Atom x5 + |

| first announced | October 26, 2016 + |

| first launched | 2017 + |

| full page name | intel/atom x5/x5-e3940 + |

| has extended page tables support | true + |

| has feature | integrated gpu +, Advanced Encryption Standard Instruction Set Extension +, Burst Performance Technology +, Enhanced SpeedStep Technology + and Extended Page Tables + |

| has intel burst performance technology | true + |

| has intel enhanced speedstep technology | true + |

| has locked clock multiplier | true + |

| has second level address translation support | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| instance of | microprocessor + |

| integrated gpu | HD Graphics 500 + |

| integrated gpu base frequency | 400 MHz (0.4 GHz, 400,000 KHz) + |

| integrated gpu max frequency | 600 MHz (0.6 GHz, 600,000 KHz) + |

| integrated gpu max memory | 2,048 MiB (2,097,152 KiB, 2,147,483,648 B, 2 GiB) + |

| l1d$ description | 6-way set associative + |

| l1d$ size | 48 KiB (49,152 B, 0.0469 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l2$ description | 16-way set associative + |

| l2$ size | 2 MiB (2,048 KiB, 2,097,152 B, 0.00195 GiB) + |

| l3$ description | No L3$ + |

| l3$ size | 0 MiB (0 KiB, 0 B, 0 GiB) + |

| ldate | 2017 + |

| main image |  + + |

| manufacturer | Intel + |

| market segment | Embedded + |

| max cpu count | 1 + |

| max junction temperature | 383.15 K (110 °C, 230 °F, 689.67 °R) + |

| max memory | 8,192 MiB (8,388,608 KiB, 8,589,934,592 B, 8 GiB, 0.00781 TiB) + |

| max pcie lanes | 4 + |

| microarchitecture | Goldmont + |

| min junction temperature | 233.15 K (-40 °C, -40 °F, 419.67 °R) + |

| model number | x5-E3940 + |

| name | Intel Atom x5-E3940 + |

| platform | Apollo Lake + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| series | E3900 + |

| smp max ways | 1 + |

| tdp | 9.5 W (9,500 mW, 0.0127 hp, 0.0095 kW) + |

| technology | CMOS + |

| thread count | 4 + |

| turbo frequency (1 core) | 1,800 MHz (1.8 GHz, 1,800,000 kHz) + |

| word size | 64 bit (8 octets, 16 nibbles) + |