m (Bot: moving all {{mpu}} to {{chip}}) |

|||

| Line 1: | Line 1: | ||

{{cmu title|PipeRench}} | {{cmu title|PipeRench}} | ||

| − | {{ | + | {{chip |

| name = PipeRench | | name = PipeRench | ||

| image = cmu piperench logo.gif | | image = cmu piperench logo.gif | ||

Latest revision as of 15:13, 13 December 2017

| Edit Values | |

| PipeRench | |

| Logo | |

| General Info | |

| Designer | Carnegie Mellon University |

| Introduction | April, 2000 (announced) 2002 (launched) |

| General Specs | |

| Frequency | 120 MHz |

| Bus speed | 60 MHz |

| Clock multiplier | 2 |

| Microarchitecture | |

| Process | 180 nm |

| Transistors | 3,650,000 |

| Technology | CMOS |

| Die | 49 mm² |

| Electrical | |

| Power dissipation | 4 W |

PipeRench was a research microprocessor designed at Carnegie Mellon University in the early 2000s. PipeRench was developed with a reconfigurable pipeline. This allows what would otherwise have to be implemented as specialized embedded chips to be implemented in a more generic way using PipeRench through reconfiguration.

Technology developed for this project was eventually leased to Rapport for their Kilocore architecture which eventually resulted in the KC256, a 256-core chip.

Architecture[edit]

PipeRench is designed as a reconfigurable fabric. The chip breaks down each of its pipeline stages into individual stripes. Each strip has a set of simple execution units (EU/PE), register files, and a interconnection network. By configuring each of the stripes using the interconnect network, it's possible to virtualize different kind of custom hardware. The ALU, for example contains additional circuitry to facilitate bit-slicing.

| This section requires expansion; you can help adding the missing info. |

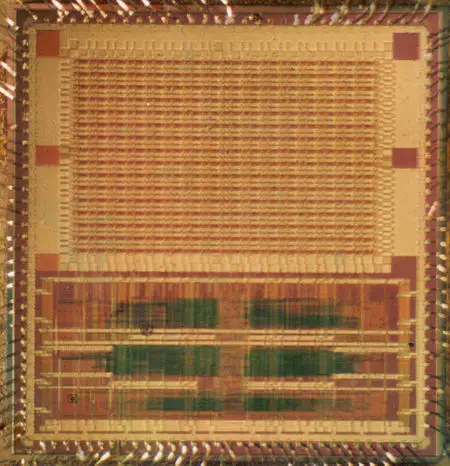

Die Shot[edit]

49 mm² on a 180 nm process.

Documents[edit]

- Seth C. Goldstein, Herman Schmit, Mihai Budiu, Srihari Cadambi, Matt Moe, and R. Reed Taylor, "PipeRench: A Reconfigurable Architecture and Compiler", April 2000, Carnegie Mellon University Computer Science Department.

External links[edit]

| base frequency | 120 MHz (0.12 GHz, 120,000 kHz) + |

| bus speed | 60 MHz (0.06 GHz, 60,000 kHz) + |

| clock multiplier | 2 + |

| designer | Carnegie Mellon University + |

| die area | 49 mm² (0.076 in², 0.49 cm², 49,000,000 µm²) + |

| first announced | April 2000 + |

| first launched | 2002 + |

| full page name | cmu/piperench + |

| instance of | microprocessor + |

| ldate | 2002 + |

| main image |  + + |

| main image caption | Logo + |

| name | PipeRench + |

| power dissipation | 4 W (4,000 mW, 0.00536 hp, 0.004 kW) + |

| process | 180 nm (0.18 μm, 1.8e-4 mm) + |

| technology | CMOS + |

| transistor count | 3,650,000 + |