From WikiChip

Difference between revisions of "intel/tick-tock"

(→Schedule) |

(→Timeline Slides) |

||

| (9 intermediate revisions by 2 users not shown) | |||

| Line 4: | Line 4: | ||

Under the Tick-Tock Model: | Under the Tick-Tock Model: | ||

| − | * '''Tick''' - With each tick, Intel advances their manufacturing [[process technology]] in line with [[Moore's Law]]. Each new [[process technology|process]] introduces higher [[transistor density]] and a generally a plethora of other advantages such as higher performance and lower power consumption. During a tick, Intel retrofits {{intel|microarchitectures|their previous}} [[microarchitecture]] to the new process which inherently yielded better performance and energy saving. | + | * '''Tick''' - With each tick, Intel advances their manufacturing [[process technology]] in line with [[Moore's Law]]. Each new [[process technology|process]] introduces higher [[transistor density]] and a generally a plethora of other advantages such as higher performance and lower power consumption. During a tick, Intel retrofits {{intel|microarchitectures|their previous}} [[microarchitecture]] to the new process which inherently yielded better performance and energy saving. At this phase, only lightweight features and improvements are introduced. |

| − | * '''Tock''' - With each tock, Intel uses the their latest [[manufacturing process technology]] from their "tick" to manufacture a newly designed [[microarchitecture]]. The new microarchitecture is designed with the new process in mind and typically introduces Intel's newest big features and functionalities. | + | * '''Tock''' - With each tock, Intel uses the their latest [[manufacturing process technology]] from their "tick" to manufacture a newly designed [[microarchitecture]]. The new microarchitecture is designed with the new process in mind and typically introduces Intel's newest big features and functionalities. New [[instruction set|instructions]] are often added during this cycle stage. |

| − | == | + | == Roadmap == |

{| class="wikitable" | {| class="wikitable" | ||

| − | ! colspan="4" style="background:#D6D6FF;" | Intel Tick-Tock | + | ! colspan="4" style="background:#D6D6FF;" | Intel Tick-Tock Roadmap |

|- | |- | ||

!Cycle !! [[technology node|Process]] !! Introduction !! Microarchitecture | !Cycle !! [[technology node|Process]] !! Introduction !! Microarchitecture | ||

|- | |- | ||

| − | | Tick || [[65 nm]] || 2006 || {{intel|microarchitectures/Core|Core}} | + | | Tick || [[65 nm]] || 2005 || Pentium D |

| + | |- | ||

| + | | Tock || [[65 nm]] || 2006 || {{intel|microarchitectures/Core|Core}} | ||

|- | |- | ||

| Tick || [[45 nm]] || 2007 || {{intel|microarchitectures/Penryn|Penryn}} | | Tick || [[45 nm]] || 2007 || {{intel|microarchitectures/Penryn|Penryn}} | ||

| Line 32: | Line 34: | ||

| Tock || [[14 nm]] || 2015 || {{intel|microarchitectures/Skylake|Skylake}} | | Tock || [[14 nm]] || 2015 || {{intel|microarchitectures/Skylake|Skylake}} | ||

|} | |} | ||

| + | |||

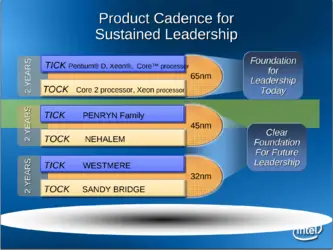

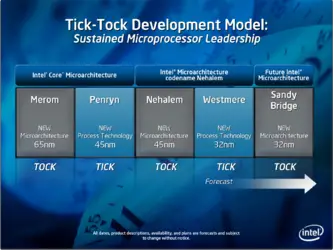

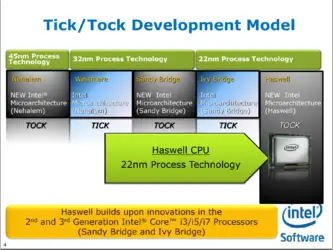

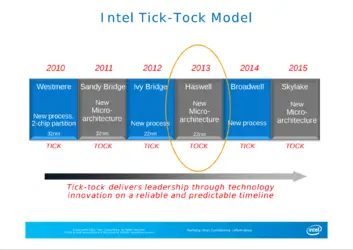

| + | == Timeline Slides == | ||

| + | <gallery heights="250px" widths="357px"> | ||

| + | File:tick-tock (2008).png | ||

| + | File:tick-tock (2009).png | ||

| + | File:tick-tock (2012).png | ||

| + | File:tick-tock (2013).png | ||

| + | File:tick-tock (2014).png | ||

| + | File:tick-tock (2014, 2).png | ||

| + | </gallery> | ||

| + | |||

| + | [[Category:intel]] | ||

Latest revision as of 22:13, 30 April 2017

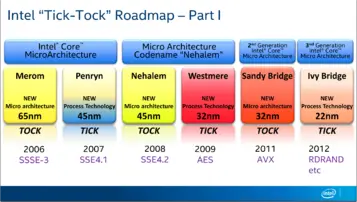

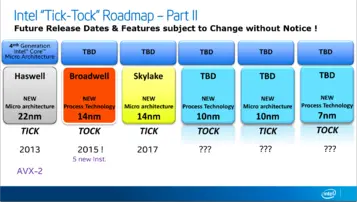

Tick-Tock was an aggressive development model introduced by Intel for their mainstream microprocessors in 2005 and phased out in 2016 whereby microarchitecture changes were in-sync with their process shrink. Under the tick-tock scheme roughly every 12-18 months the Intel alternated between "Tick" and "Tock". Intel no longer uses this model, instead they use the Process-Architecture-Optimization (PAO).

Under the Tick-Tock Model:

- Tick - With each tick, Intel advances their manufacturing process technology in line with Moore's Law. Each new process introduces higher transistor density and a generally a plethora of other advantages such as higher performance and lower power consumption. During a tick, Intel retrofits their previous microarchitecture to the new process which inherently yielded better performance and energy saving. At this phase, only lightweight features and improvements are introduced.

- Tock - With each tock, Intel uses the their latest manufacturing process technology from their "tick" to manufacture a newly designed microarchitecture. The new microarchitecture is designed with the new process in mind and typically introduces Intel's newest big features and functionalities. New instructions are often added during this cycle stage.

Roadmap[edit]

| Intel Tick-Tock Roadmap | |||

|---|---|---|---|

| Cycle | Process | Introduction | Microarchitecture |

| Tick | 65 nm | 2005 | Pentium D |

| Tock | 65 nm | 2006 | Core |

| Tick | 45 nm | 2007 | Penryn |

| Tock | 45 nm | 2008 | Nehalem |

| Tick | 32 nm | 2009 | Westmere |

| Tock | 32 nm | 2010 | Sandy Bridge |

| Tick | 22 nm | 2011 | Ivy Bridge |

| Tock | 22 nm | 2013 | Haswell |

| Tick | 14 nm | 2014 | Broadwell |

| Tock | 14 nm | 2015 | Skylake |