From WikiChip

Difference between revisions of "intel/microarchitectures/golden cove"

(Redwood Cove in Meteor Lake is the successor) |

|||

| (23 intermediate revisions by 12 users not shown) | |||

| Line 5: | Line 5: | ||

|designer=Intel | |designer=Intel | ||

|manufacturer=Intel | |manufacturer=Intel | ||

| − | |introduction=2021 | + | |introduction=November 4, 2021 |

| − | |process= | + | |process=10nm |

|isa=x86-64 | |isa=x86-64 | ||

| + | |core name=Alder Lake, Sapphire Rapids | ||

|predecessor=Willow Cove | |predecessor=Willow Cove | ||

|predecessor link=intel/microarchitectures/willow cove | |predecessor link=intel/microarchitectures/willow cove | ||

| − | |successor= | + | |predecessor 2=Cypress Cove |

| − | |successor link=intel/microarchitectures/ | + | |predecessor 2 link=intel/microarchitectures/rocket lake |

| + | |successor=Redwood Cove | ||

| + | |successor link=intel/microarchitectures/redwood cove | ||

}} | }} | ||

| − | '''Golden Cove''' is the successor to {{\\|Willow Cove}}, a high-performance [[10 | + | '''Golden Cove''' is the successor to {{\\|Willow Cove}}, a high-performance [[10 nm]] [[x86]] core microarchitecture designed by [[Intel]] for an array of server and client products, including Sapphire Rapids (server) and Alder Lake (client). |

== History == | == History == | ||

| Line 20: | Line 23: | ||

== Process Technology == | == Process Technology == | ||

| − | Intel has | + | Intel has confirmed that the Golden Cove architecture will be fabricated on their Intel 7 process (previously 10 nm Enhanced SuperFin (ESF)). |

== Architecture == | == Architecture == | ||

=== Key changes from {{\\|Willow Cove}}=== | === Key changes from {{\\|Willow Cove}}=== | ||

| − | {{ | + | * Performance improvements |

| + | ** Strong IPC improvement (19%) | ||

| + | ** AI workload improvement (AMX) | ||

| + | ** Network/5G performance improvements | ||

| + | * New security features | ||

| + | * Front-End | ||

| + | ** Add 2 simple decoders from 5 but canceled the complex decoder design as it is no longer practical and complex instructions can now be handled by macro uop fusion independently in instruction sequencer, total is now 6 simple decoders | ||

| + | ** x2.5 BTB at 12K entries | ||

| + | ** 2x pages 4k | ||

| + | ** Add more 256 and 32 pages of 2M and 4MB respectively | ||

| + | * Back-End | ||

| + | ** Increased ROB 512 (from 352 Sunny Cove) | ||

| + | ** Add 2 execution port for a total 12 | ||

| + | * Execution Engine | ||

| + | ** Add one ALU and LEA for a total 5 | ||

| + | {{expand list}} | ||

| + | |||

| + | == Bibliography == | ||

| + | * Intel Architecture Day 2018, December 11, 2018 | ||

| + | * Intel Details Golden Cove: Next-Generation Big Core For Client and Server SoCs | ||

Latest revision as of 20:57, 12 June 2024

| Edit Values | |

| Golden Cove µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | November 4, 2021 |

| Process | 10nm |

| Instructions | |

| ISA | x86-64 |

| Cores | |

| Core Names | Alder Lake, Sapphire Rapids |

| Succession | |

Golden Cove is the successor to Willow Cove, a high-performance 10 nm x86 core microarchitecture designed by Intel for an array of server and client products, including Sapphire Rapids (server) and Alder Lake (client).

Contents

[hide]History[edit]

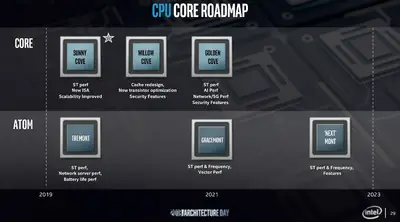

Golden Cove was originally unveiled by Intel at their 2018 architecture day. Golden Cove is intended to succeed Willow Cove in the 2021 timeframe.

Process Technology[edit]

Intel has confirmed that the Golden Cove architecture will be fabricated on their Intel 7 process (previously 10 nm Enhanced SuperFin (ESF)).

Architecture[edit]

Key changes from Willow Cove[edit]

- Performance improvements

- Strong IPC improvement (19%)

- AI workload improvement (AMX)

- Network/5G performance improvements

- New security features

- Front-End

- Add 2 simple decoders from 5 but canceled the complex decoder design as it is no longer practical and complex instructions can now be handled by macro uop fusion independently in instruction sequencer, total is now 6 simple decoders

- x2.5 BTB at 12K entries

- 2x pages 4k

- Add more 256 and 32 pages of 2M and 4MB respectively

- Back-End

- Increased ROB 512 (from 352 Sunny Cove)

- Add 2 execution port for a total 12

- Execution Engine

- Add one ALU and LEA for a total 5

This list is incomplete; you can help by expanding it.

Bibliography[edit]

- Intel Architecture Day 2018, December 11, 2018

- Intel Details Golden Cove: Next-Generation Big Core For Client and Server SoCs

Facts about "Golden Cove - Microarchitectures - Intel"

| codename | Golden Cove + |

| designer | Intel + |

| first launched | November 4, 2021 + |

| full page name | intel/microarchitectures/golden cove + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Golden Cove + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |