From WikiChip

File list

This special page shows all uploaded files.

First page |

Previous page |

Next page |

Last page |

| Date | Name | Thumbnail | Size | User | Description | Versions |

|---|---|---|---|---|---|---|

| 21:03, 6 September 2017 | hisilicon kirin logo.svg (file) | 5 KB | Inject | HiSilicon {{hisil|Kirin}} logo | 1 | |

| 00:47, 7 September 2017 | kirin 970.png (file) |  |

1.76 MB | Inject | HiSilicon Kirin 970. Image by Huawei | 1 |

| 13:43, 7 September 2017 | kirin 970 npu.png (file) |  |

765 KB | Inject | NPU performance shown by Mr. Yu during 2017 IFA. Image from Huawei stream. | 1 |

| 20:15, 7 September 2017 | sandy bridge chop layout.png (file) |  |

311 KB | David | Intel {{intel|Sandy Bridge|l=arch}} chop layout. Image by Intel. | 1 |

| 23:07, 7 September 2017 | sandy bridge core die.png (file) |  |

405 KB | David | Intel {{intel|Sandy Bridge|l=arch}} core. Cut out from the Intel Sandy Bridge quad-core die shot. * Annotated Version File:sandy_bridge_core_die_(annotated).png | 1 |

| 23:07, 7 September 2017 | sandy bridge core die (annotated).png (file) |  |

408 KB | David | Intel {{intel|Sandy Bridge|l=arch}} core annotated by WikiChip. Cut out from the Intel Sandy Bridge quad-core die shot. * Original Version: File:sandy_bridge_core_die.png | 1 |

| 23:25, 7 September 2017 | sandy bridge 4x core complex die.png (file) |  |

2.43 MB | David | A group of 4 cores from a {{intel|Sandy Bridge|l=arch}} die. Image by Intel | 1 |

| 16:46, 8 September 2017 | sandy bridge (dual-core).jpg (file) |  |

194 KB | Nible | artist render of dual core sandy bridge die | 1 |

| 01:11, 9 September 2017 | sandy bridge soc block diagram (dual).svg (file) |  |

18 KB | At32Hz | 2 | |

| 01:11, 9 September 2017 | sandy bridge soc block diagram.svg (file) | 27 KB | At32Hz | 2 | ||

| 12:58, 9 September 2017 | sandy bridge clock domains.png (file) |  |

64 KB | David | Intel {{intel|Sandy Bridge}} clock domains. | 1 |

| 13:16, 9 September 2017 | sandy bridge bclk.png (file) |  |

480 KB | David | Intel {{intel|Sandy Bridge}} BCLK capabilities. Image by Intel. | 1 |

| 15:48, 9 September 2017 | core-overview-of-2nd-generation-intel-core-processor-family-brief.pdf (file) |  |

1.28 MB | Inject | 2nd Generation Intel® Core Processor Family | 1 |

| 15:48, 9 September 2017 | performance-2nd-gen-core-product-brief.pdf (file) |  |

1.54 MB | Inject | 2nd Generation Intel® Core vPro Processor Family | 1 |

| 15:48, 9 September 2017 | performance-2nd-generation-core-vpro-family-paper.pdf (file) |  |

3.32 MB | Inject | 2nd Generation Intel® Core vPro Processor Family New levels of security, manageability, and responsiveness White Paper * 2nd Gen Intel® Core i7 vPro Processor * 2nd Gen Intel® Core i5 vPro Processor | 1 |

| 17:27, 9 September 2017 | oracle roadmap (jan 2017).png (file) |  |

232 KB | At32Hz | Oracle roadmap, January 2017. | 1 |

| 17:28, 9 September 2017 | oracle roadmap (sept 2017).png (file) |  |

199 KB | At32Hz | Oracle roadmap, September 2017. | 1 |

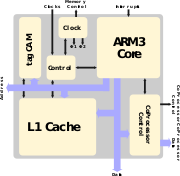

| 22:13, 9 September 2017 | arm3 block diagram.svg (file) |  |

25 KB | At32Hz | A little more specific than just 'RAM' | 3 |

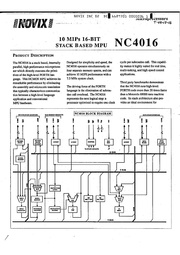

| 07:51, 10 September 2017 | nc4016.pdf (file) |  |

235 KB | ChipIt | Novix {{novix|NC4016}} | 1 |

| 15:12, 10 September 2017 | helio p30.png (file) |  |

385 KB | Inject | 2 | |

| 15:12, 10 September 2017 | helio p23.png (file) |  |

385 KB | Inject | 2 | |

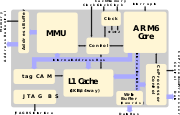

| 17:43, 11 September 2017 | arm610 block diagram.svg (file) |  |

36 KB | At32Hz | 2 | |

| 04:27, 12 September 2017 | sandy bridge die area (quad).svg (file) |  |

13 KB | At32Hz | Die area breakdown of {{intel|Sandy Bridge|l=arch}}, quad-core version. | 1 |

| 04:55, 12 September 2017 | sandy bridge die area (dual, gt1).svg (file) |  |

11 KB | At32Hz | Breakdown of the die area of a {{intel|Sandy Bridge|l=arch}} dual-core GT1 die. | 1 |

| 04:55, 12 September 2017 | sandy bridge die area (dual, gt2).svg (file) |  |

10 KB | At32Hz | Breakdown of the die area of a {{intel|Sandy Bridge|l=arch}} dual-core GT2 die. | 1 |

| 22:03, 12 September 2017 | a11 intro keynote event.png (file) |  |

803 KB | Inject | Apple {{apple|A11}} intro slide from Apple's Keynote Event September 2017. | 1 |

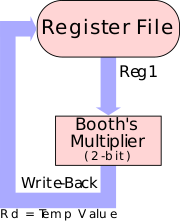

| 21:59, 13 September 2017 | arm2 mul cycle.svg (file) |  |

7 KB | At32Hz | {{acorn|ARM2|l=arch}} multiplication mid-way | 1 |

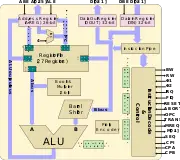

| 23:05, 13 September 2017 | arm2 block diagram.svg (file) |  |

76 KB | At32Hz | more detail for multiplier | 4 |

| 23:08, 13 September 2017 | arm6 block diagram.svg (file) |  |

77 KB | At32Hz | added multiplier detail | 3 |

| 14:42, 14 September 2017 | microsoft logo (2012).svg (file) | 3 KB | David | Microsoft logo | 1 | |

| 17:08, 14 September 2017 | scorpio engine (front).png (file) |  |

571 KB | David | Microsoft {{microsoft|Scorpio Engine}} | 1 |

| 21:53, 14 September 2017 | scorpio engine die shot.png (file) |  |

1.22 MB | David | AMD {{amd|Scorpio Engine|l=arch}} for the {{microsoft|Scorpio Engine}} chip. | 1 |

| 00:31, 15 September 2017 | scorpio engine die shot (annotated).png (file) |  |

1.06 MB | David | annotated version of the AMD {{amd|Scorpio Engine|l=arch}} for the {{microsoft|Scorpio Engine}} chip. * Original version: File:scorpio engine die shot.png | 1 |

| 10:30, 19 September 2017 | oracle logo.svg (file) | 6 KB | At32Hz | Oracle logo | 1 | |

| 00:25, 21 September 2017 | scorpio engine block diagram.png (file) |  |

216 KB | At32Hz | {{microsoft|Scorpio Engine|l=arch}} Block Diagram by Microsoft. | 1 |

| 01:36, 21 September 2017 | scorpio engine rb-mem subsys.svg (file) |  |

80 KB | At32Hz | 2 | |

| 13:18, 22 September 2017 | sandy bridge vcc min improvements.png (file) |  |

74 KB | David | Improvements done to lower the Vcc Min of the L3 in Intel's {{intel|Sandy Bridge}} | 1 |

| 13:28, 22 September 2017 | sandy bridge register file shared strength and post silicon tuning.png (file) | 168 KB | David | A technique used in Intel's {{intel|Sandy Bridge|l=arch}} in order to reduce the minimum voltage required. Tuning also includes three resistors for post-silicon tuning. | 1 | |

| 00:20, 23 September 2017 | sandy bridge ring scalability.svg (file) |  |

13 KB | David | minor correction to where the ring goes. | 2 |

| 05:46, 24 September 2017 | AMD Naples SoC.svg (file) |  |

449 KB | At32Hz | rm prev mem image in favor of a light-weight one | 3 |

| 05:48, 24 September 2017 | AMD Summit Ridge SoC.svg (file) |  |

171 KB | At32Hz | changed old mem in favor of a light-weight one | 2 |

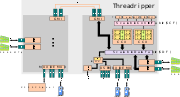

| 06:00, 24 September 2017 | AMD Threadripper SoC.svg (file) |  |

362 KB | At32Hz | AMD {{amd|Zen|l=arch}}-based {{amd|Threadripper}} SoC block diagram | 1 |

| 06:24, 24 September 2017 | x399 platform.png (file) |  |

1.25 MB | At32Hz | AMD {{amd|Threadripper}} (x399) platform | 1 |

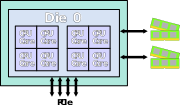

| 07:08, 24 September 2017 | zen-1zep.svg (file) |  |

21 KB | At32Hz | AMD {{amd|Zen|l=arch}} 1-{{amd|Zen#Modules (Zeppelin)|Zeppelin|l=arch}} Config. | 1 |

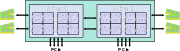

| 07:08, 24 September 2017 | zen-2zep.svg (file) |  |

44 KB | At32Hz | AMD {{amd|Zen|l=arch}} 2-{{amd|Zen#Modules (Zeppelin)|Zeppelin|l=arch}} Config. | 1 |

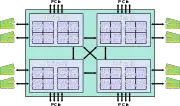

| 07:08, 24 September 2017 | zen-4zep.svg (file) |  |

83 KB | At32Hz | AMD {{amd|Zen|l=arch}} 4-{{amd|Zen#Modules (Zeppelin)|Zeppelin|l=arch}} Config. | 1 |

| 07:17, 24 September 2017 | threadripper top 5 percent of dies.png (file) |  |

174 KB | At32Hz | AMD {{amd|Ryzen Threadripper}} is top 5% of dies. | 1 |

| 07:29, 24 September 2017 | amd if data fabric.png (file) |  |

1.59 MB | At32Hz | AMD {{amd|Infinity Fabric}} Data Fabric | 1 |

| 08:11, 24 September 2017 | zen numa.png (file) |  |

1.4 MB | At32Hz | AMD {{amd|Zen|l=arch}} NUMA mode. | 1 |

| 08:11, 24 September 2017 | zen uma.png (file) |  |

1.41 MB | At32Hz | AMD {{amd|Zen|l=arch}} UMA mode. | 1 |

First page |

Previous page |

Next page |

Last page |