From WikiChip

Information for "intel/cores/kaby lake x"

Basic information

| Display title | Kaby Lake X - Cores - Intel |

| Default sort key | Kaby Lake X, Intel |

| Page length (in bytes) | 3,064 |

| Page ID | 16618 |

| Page content language | English (en) |

| Page content model | wikitext |

| Indexing by robots | Allowed |

| Number of redirects to this page | 4 |

| Counted as a content page | Yes |

| Number of subpages of this page | 0 (0 redirects; 0 non-redirects) |

Page protection

| Edit | Allow all users (infinite) |

| Move | Allow all users (infinite) |

Edit history

| Page creator | At32Hz (talk | contribs) |

| Date of page creation | 00:07, 24 January 2017 |

| Latest editor | David (talk | contribs) |

| Date of latest edit | 09:07, 24 October 2018 |

| Total number of edits | 26 |

| Total number of distinct authors | 5 |

| Recent number of edits (within past 90 days) | 0 |

| Recent number of distinct authors | 0 |

Page properties

| Transcluded templates (16) | Templates used on this page:

|

Facts about "Kaby Lake X - Cores - Intel"

| designer | Intel + |

| first announced | May 30, 2017 + |

| first launched | June 26, 2017 + |

| instance of | core + |

| isa | x86-64 + |

| isa family | x86 + |

| main image |  + and + and  + + |

| manufacturer | Intel + |

| microarchitecture | Kaby Lake + |

| name | Kaby Lake X + |

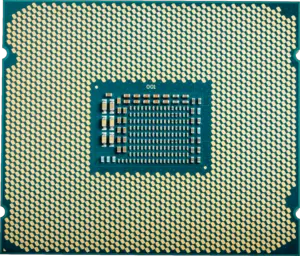

| package | FCLGA-2066 + |

| platform | Basin Falls + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| socket | Socket R4 + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |