From WikiChip

Revision history of "pezy/pezy-1"

Diff selection: Mark the radio boxes of the revisions to compare and hit enter or the button at the bottom.

Legend: (cur) = difference with latest revision, (prev) = difference with preceding revision, m = minor edit.

Facts about "PEZY-1 - PEZY"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | PEZY-1 - PEZY#io + |

| base frequency | 533.33 MHz (0.533 GHz, 533,330 kHz) + |

| core count | 512 + |

| designer | PEZY + |

| die area | 335 mm² (0.519 in², 3.35 cm², 335,000,000 µm²) + |

| die length | 16.8 mm (1.68 cm, 0.661 in, 16,800 µm) + |

| die width | 21 mm (2.1 cm, 0.827 in, 21,000 µm) + |

| first announced | 2011 + |

| first launched | 2012 + |

| full page name | pezy/pezy-1 + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| l1$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l1d$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l2$ size | 1 MiB (1,024 KiB, 1,048,576 B, 9.765625e-4 GiB) + |

| ldate | 2012 + |

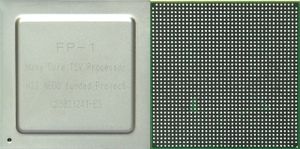

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Industrial + |

| max memory bandwidth | 39.74 GiB/s (40,693.76 MiB/s, 42.671 GB/s, 42,670.5 MB/s, 0.0388 TiB/s, 0.0427 TB/s) + |

| max memory channels | 4 + |

| max pcie lanes | 24 + |

| model number | PEZY-1 + |

| name | PEZY-1 + |

| power dissipation | 35 W (35,000 mW, 0.0469 hp, 0.035 kW) + |

| process | 40 nm (0.04 μm, 4.0e-5 mm) + |

| supported memory type | DDR3-1333 + |

| technology | CMOS + |