-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

Revision history of "intel/cores/kaby lake u"

Diff selection: Mark the radio boxes of the revisions to compare and hit enter or the button at the bottom.

Legend: (cur) = difference with latest revision, (prev) = difference with preceding revision, m = minor edit.

Retrieved from "https://en.wikichip.org/wiki/intel/cores/kaby_lake_u"

Facts about "Kaby Lake U - Cores - Intel"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Kaby Lake U - Cores - Intel#package + |

| designer | Intel + |

| first announced | August 30, 2016 + |

| first launched | August 30, 2016 + |

| instance of | core + |

| isa | x86-64 + |

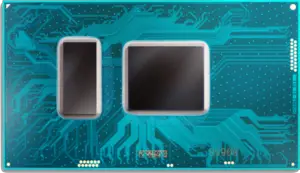

| main image |  + and + and  + + |

| main image caption | 3-die config Iris Plus KBL-U (with OPC) + and 2-die config KBL-U + |

| manufacturer | Intel + |

| microarchitecture | Kaby Lake + |

| name | Kaby Lake U + |

| package | FCBGA-1356 + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |