From WikiChip

Exynos M5 - Microarchitectures - Samsung

| Edit Values | |

| Exynos M5 (Lion) µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Samsung |

| Manufacturer | Samsung |

| Introduction | 2020 |

| Process | 7 nm |

| Core Configs | 2 |

| Pipeline | |

| Type | Superscalar, Superpipeline |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Stages | 16 |

| Decode | 6-way |

| Instructions | |

| ISA | ARMv8.2 |

| Cache | |

| L1I Cache | 64 KiB/core 4-way set associative |

| L1D Cache | 64 KiB/core 8-way set associative |

| L2 Cache | 512 KiB/core 8-way set associative |

| L3 Cache | 2 MiB/cluster 16-way set associative |

| Succession | |

Exynos M5 (Lion) <aka Mongoose 5 > is the successor to the Exynos M4 (Cheetah) <aka Mongoose 4 >, a 7 nm ARM microarchitecture designed by Samsung for their consumer electronics.

Contents

Process Technology[edit]

The M5 is fabricated on Samsung's 7 nm process (7LPP).

Compiler support[edit]

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| GCC | -mcpu=exynos-m5 |

-mtune=exynos-m5

|

| LLVM | -mcpu=exynos-m5 |

-mtune=exynos-m5

|

Architecture[edit]

Key changes from M4 (Cheetah)[edit]

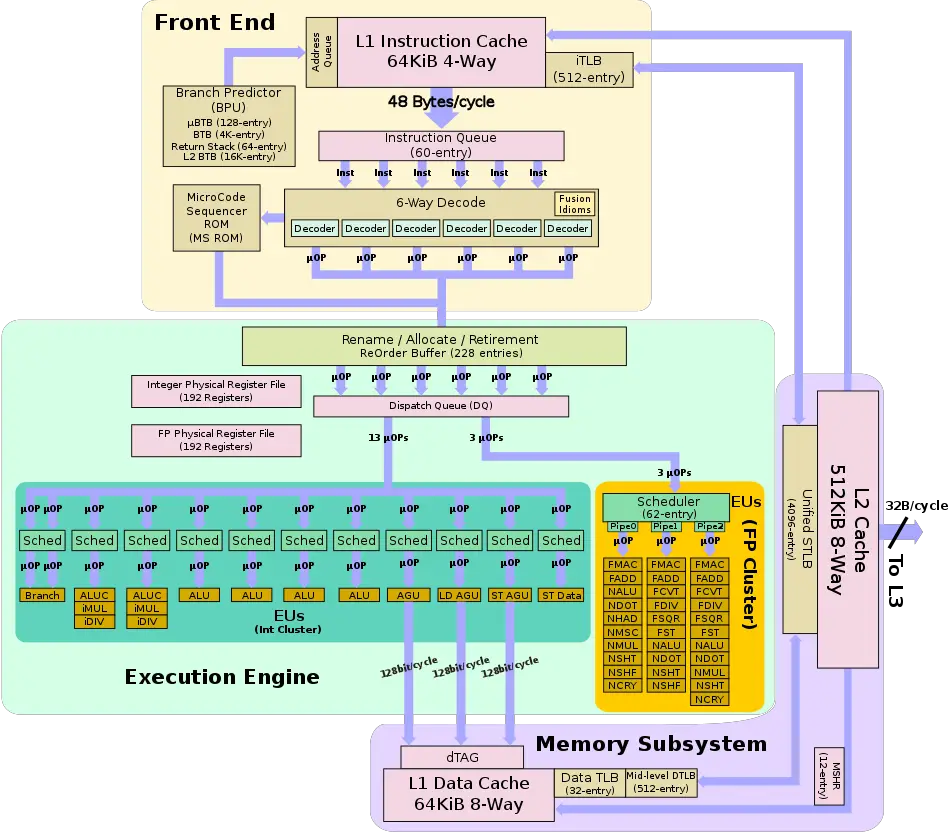

- Front end

- Larger instruction queue (60 entries, up from 48)

- Improved mispredict penalty (15 cycles, down from 16)

- Back end

- LSU execution units reorganized

- Two new 32b integer ALU pipes

- Floating-point execution units reorganized

- Three new dedicted NEON dot product EUs

- LSU execution units reorganized

This list is incomplete; you can help by expanding it.

Block Diagram[edit]

Individual Core[edit]

Memory Hierarchy[edit]

|

The M3 TLB consists of dedicated L1 TLB for instruction

|

All M5 Processors[edit]

| List of M5-based Processors | |||||||

|---|---|---|---|---|---|---|---|

| Main processor | Integrated Graphics | ||||||

| Model | Family | Launched | Arch | Cores | Frequency | GPU | Frequency |

| 990 | Exynos | 2020 | Mongoose 5, Cortex-A76, Cortex-A55 | 8 | 2.6 GHz 2,600 MHz , 3 GHz2,600,000 kHz 3,000 MHz , 2.1 GHz3,000,000 kHz 2,100 MHz 2,100,000 kHz | Mali-G77 | 832 MHz 0.832 GHz 832,000 KHz |

| Count: 1 | |||||||

Bibliography[edit]

- LLVM: lib/Target/AArch64/AArch64SchedExynosM5.td

Facts about "Exynos M5 - Microarchitectures - Samsung"

| codename | Exynos M5 (Lion) + |

| core count | 2 + |

| designer | Samsung + |

| first launched | 2020 + |

| full page name | samsung/microarchitectures/m5 + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8.2 + |

| manufacturer | Samsung + |

| microarchitecture type | CPU + |

| name | Exynos M5 (Lion) + |

| pipeline stages | 16 + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + |