From WikiChip

Atom Z500 - Intel

| Edit Values | |||||||||

| Atom Z500 | |||||||||

| |||||||||

| Silverthorne chip | |||||||||

| General Info | |||||||||

| Designer | Intel | ||||||||

| Manufacturer | Intel | ||||||||

| Model Number | Z500 | ||||||||

| Part Number | AC80586UC800DE, AC80566UC800DE | ||||||||

| S-Spec | SLB6Q QGZU (QS), QGXC (QS) | ||||||||

| Market | Mobile | ||||||||

| Introduction | April 2, 2008 (announced) April 2, 2008 (launched) | ||||||||

| Release Price | $45 | ||||||||

| Shop | Amazon | ||||||||

| General Specs | |||||||||

| Family | Atom | ||||||||

| Series | Z500 | ||||||||

| Locked | Yes | ||||||||

| Frequency | 800 MHz | ||||||||

| Bus type | FSB | ||||||||

| Bus speed | 100 MHz | ||||||||

| Bus rate | 400 MT/s | ||||||||

| Clock multiplier | 8 | ||||||||

| CPUID | 106C2 | ||||||||

| Microarchitecture | |||||||||

| ISA | x86-32 (x86) | ||||||||

| Microarchitecture | Bonnell | ||||||||

| Platform | Menlow | ||||||||

| Chipset | Poulsbo | ||||||||

| Core Name | Silverthorne | ||||||||

| Core Family | 6 | ||||||||

| Core Model | 28 | ||||||||

| Core Stepping | C0 | ||||||||

| Process | 45 nm | ||||||||

| Transistors | 47,212,207 | ||||||||

| Technology | CMOS | ||||||||

| Die | 24.18 mm² 7.8 mm × 3.1 mm | ||||||||

| Word Size | 32 bit | ||||||||

| Cores | 1 | ||||||||

| Threads | 2 | ||||||||

| Multiprocessing | |||||||||

| Max SMP | 1-Way (Uniprocessor) | ||||||||

| Electrical | |||||||||

| Power dissipation (average) | 160 mW | ||||||||

| Power (idle) | 80 mW | ||||||||

| Vcore | 0.80 V-1.1 V | ||||||||

| SDP | 960 mW | ||||||||

| TDP | 650 mW | ||||||||

| Tjunction | 0 °C – 90 °C | ||||||||

| Tcase | 0 °C – 70 °C | ||||||||

| Tstorage | -40 °C – 85 °C | ||||||||

| Packaging | |||||||||

| |||||||||

Z500 is an ultra-low power 32-bit x86 microprocessor introduced by Intel in early 2008 specifically for Mobile Internet Devices (MID). The Z500, which is based on the Bonnell microarchitecture (Silverthorne core), is manufactured on a 45 nm process. This processor operates at 800 MHz with a TDP of just 650 mW and an average power of 160 mW. The MPU features a legacy 400 MT/s front-side bus capable of communicating with the Poulsbo chipset in both low-power CMOS mode as well as normal GTL mode (which also works with other chipsets).

Model price includes the chipset.

Contents

Cache[edit]

- Main article: Bonnell § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller[edit]

This processor has no integrated memory controller.

Graphics[edit]

This processor has no integrated graphics.

Features[edit]

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||

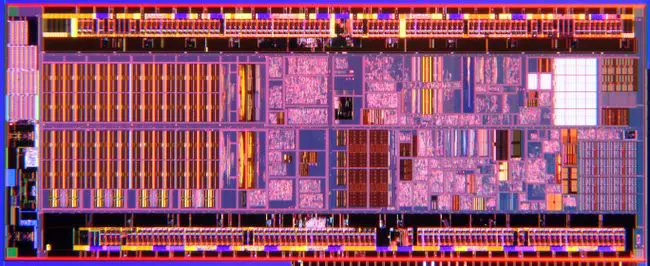

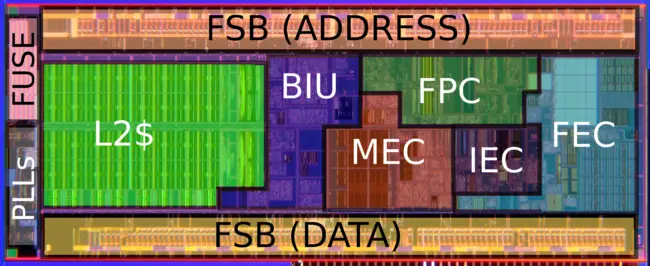

Die Shot[edit]

- See also: Bonnell § Silverthorne Die

- 45 nm process

- 9 metal layers

- 47,212,207 transistors

- 3.1 mm x 7.8 mm

- 24.18 mm² die size

Documents[edit]

Datasheet[edit]

- Intel Atom Processor Z5xx Series Datasheet, June 2010

- Intel Atom Processor Z5xx Series Datasheet Specification Update, July 2014

Other[edit]

- Atom Z5xx Product Brief, 2008

Facts about "Atom Z500 - Intel"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Atom Z500 - Intel#package + |

| base frequency | 800 MHz (0.8 GHz, 800,000 kHz) + |

| bus rate | 400 MT/s (0.4 GT/s, 400,000 kT/s) + |

| bus speed | 100 MHz (0.1 GHz, 100,000 kHz) + |

| bus type | FSB + |

| chipset | Poulsbo + |

| clock multiplier | 8 + |

| core count | 1 + |

| core family | 6 + |

| core model | 28 + |

| core name | Silverthorne + |

| core stepping | C0 + |

| core voltage (max) | 1.1 V (11 dV, 110 cV, 1,100 mV) + |

| core voltage (min) | 0.8 V (8 dV, 80 cV, 800 mV) + |

| cpuid | 106C2 + |

| designer | Intel + |

| die area | 24.18 mm² (0.0375 in², 0.242 cm², 24,180,000 µm²) + |

| die length | 7.8 mm (0.78 cm, 0.307 in, 7,800 µm) + |

| die width | 3.1 mm (0.31 cm, 0.122 in, 3,100 µm) + |

| family | Atom + |

| first announced | April 2, 2008 + |

| first launched | April 2, 2008 + |

| full page name | intel/atom/z500 + |

| has feature | Hyper-Threading Technology + and Enhanced SpeedStep Technology + |

| has intel enhanced speedstep technology | true + |

| has locked clock multiplier | true + |

| has simultaneous multithreading | true + |

| instance of | microprocessor + |

| isa | x86-32 + |

| isa family | x86 + |

| l1$ size | 56 KiB (57,344 B, 0.0547 MiB) + |

| l1d$ description | 6-way set associative + |

| l1d$ size | 24 KiB (24,576 B, 0.0234 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 32 KiB (32,768 B, 0.0313 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| ldate | April 2, 2008 + |

| main image |  + + |

| main image caption | Silverthorne chip + |

| manufacturer | Intel + |

| market segment | Mobile + |

| max case temperature | 343.15 K (70 °C, 158 °F, 617.67 °R) + |

| max cpu count | 1 + |

| max junction temperature | 363.15 K (90 °C, 194 °F, 653.67 °R) + |

| max storage temperature | 358.15 K (85 °C, 185 °F, 644.67 °R) + |

| microarchitecture | Bonnell + |

| min case temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| min junction temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| min storage temperature | 233.15 K (-40 °C, -40 °F, 419.67 °R) + |

| model number | Z500 + |

| name | Atom Z500 + |

| package | FCBGA-441 + |

| part number | AC80586UC800DE + and AC80566UC800DE + |

| platform | Menlow + |

| power dissipation (average) | 0.16 W (160 mW, 2.1456e-4 hp, 1.6e-4 kW) + |

| power dissipation (idle) | 0.08 W (80 mW, 1.0728e-4 hp, 8.0e-5 kW) + |

| process | 45 nm (0.045 μm, 4.5e-5 mm) + |

| release price | $ 45.00 (€ 40.50, £ 36.45, ¥ 4,649.85) + |

| s-spec | SLB6Q + |

| s-spec (qs) | QGZU + and QGXC + |

| sdp | 0.96 W (960 mW, 0.00129 hp, 9.6e-4 kW) + |

| series | Z500 + |

| smp max ways | 1 + |

| socket | BGA-441 + |

| tdp | 0.65 W (650 mW, 8.7165e-4 hp, 6.5e-4 kW) + |

| technology | CMOS + |

| thread count | 2 + |

| transistor count | 47,212,207 + |

| word size | 32 bit (4 octets, 8 nibbles) + |