From WikiChip

MCS-80 - Intel

| Intel MCS-80 | |

| |

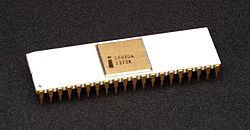

| 8080, the CPU of the MCS-80 system | |

| Developer | Intel |

| Manufacturer | Intel |

| Type | microprocessors |

| Production | 1974 |

| Release date | April, 1974 |

| Architecture | 8-bit word, 16-bit addressing |

| ISA | 8080 |

| Word size | 8 bit 1 octets

2 nibbles |

| Process | 6 μm 6,000 nm

0.006 mm |

| Technology | nMOS |

| Clock | 500 kHz-2.08 MHz |

| Package | DIP40 |

| Succession | |

| ← | → |

| MCS-8 | MCS-85 MCS-86 MCS-88 |

The MCS-80 (Micro Computer Set-80) was a family of 8-bit microprocessor chipsets developed by Intel. Introduced on April, 1974, the MCS-80 featured the 8080 CPU, the forefather of all modern x86-based microprocessors.

Contents

History[edit]

| This section is empty; you can help add the missing info by editing this page. |

Members[edit]

The original 8080 had an issue that prevented it from working with external TTL components as intended. This was fixed with the introduction of the "A" versions.

| Part | Frequency | Description |

|---|---|---|

| 8080 | 500 kHz - 2.08 MHz | MPU, Original, has compatibility issues with TTL |

| 8080A-1 | 500 kHz - 3.12 MHz | MPU |

| 8080A-2 | 500 kHz - 2.63 MHz | MPU |

| 8224 | clock generator & driver | |

| 8801 | clock generator crystal | |

| 8228 | system controller & bus driver | |

| 8238 | system controller & bus driver | |

| 8257 | Programmable DMA Controller | |

| 8259 | Programmable Interrupt Controller | |

| 8279 | Programmable Keyboard/Display Controller | |

| 8271 | Programmable Floppy Disk Controller | |

| 8222 | Dynamic RAM Refresh Controller | |

| 8205 | 1 Of 8 Binary Decoder | |

| 8210 | TTL To MOS Shifter & High Voltage Clock Driver | |

| 8212 | 8 Bit I/O Port | |

| 8214 | Priority Interrupt Control Unit | |

| 8216 | 4 Bit Parallel Bidirectional Bus Driver | |

| 8251A | Improved Programmable Communication Interface | |

| 8253 | Programmable Interval Timer | |

| 8255 | Programmable Peripheral Interface | |

| 8255A | Improved Programmable Peripheral Interface |

Military Specs[edit]

The following are military specs versions.

| Part | Frequency | Description |

|---|---|---|

| M8080A | 500 kHz - 2.08 MHz | MPU |

| M8224 | clock generator & driver | |

| M8228 | system controller & bus driver | |

| M8238 | system controller & bus driver |

Memory[edit]

Additional memory components that was used with the MCS-80

| Part | Size | Description |

|---|---|---|

| 8708 | 1024x8 bit | EPROM |

| 2716 | 2048x8 bit | EPROM (pin compatible with 2316E ROM) |

| 8308 | 1024x8 bit | MOS ROM (pin compatible with 8708 PROM) |

| 8316A | 2048x8 bit | MOS RAM |

| 2316E | 2048x8 bit | ROM |

| 2114 | 1024x4 bit | SRAM |

| 2116 | 16384x1 bit | DRAM |

Design[edit]

| This section is empty; you can help add the missing info by editing this page. |

ISA[edit]

| This section is empty; you can help add the missing info by editing this page. |

Designers[edit]

Lead designers for the MCS-80 are:

- Federico Faggin

- Masatoshi Shima

- Stan Mazor

Documents[edit]

See Also[edit]

| This article is still a stub and needs your attention. You can help improve this article by editing this page and adding the missing information. |

Facts about "MCS-80 - Intel"

| designer | Intel +, Federico Faggin +, Masatoshi Shima + and Stan Mazor + |

| full page name | intel/mcs-80 + |

| instance of | microprocessor family + |

| instruction set architecture | 8080 + |

| main designer | Intel + |

| manufacturer | Intel + |

| name | Intel MCS-80 + |

| package | DIP40 + |

| process | 6,000 nm (6 μm, 0.006 mm) + |

| technology | nMOS + |

| word size | 8 bit (1 octets, 2 nibbles) + |