-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

Cavium Coherent Processor Interconnect (CCPI) - Cavium

< cavium(Redirected from Cavium coherent processor interconnect)

| v · d · e | |

| Interconnect Architectures | |

| |

| Concepts | |

| General | |

| Peripheral | |

| Storage Devices | |

| Audio Devices | |

Cavium Coherent Processor Interconnect (CCPI') is an interconnect architecture designed by Cavium for their microprocessors.

Overview[edit]

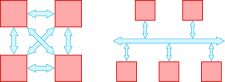

CCPI is a cache coherent interconnect architecture designed by Cavium for their various microprocessors. CCPI is used to support symmetric multiprocessing on the ThunderX and ThunderX2 families.

Data Rates[edit]

| CCPI | CCPI2 | |

|---|---|---|

| Signaling Rate | 10 GT/s | 25 GT/s |

| Lanes/Link | 24 | 24 |

| Rate/Link | 30 GB/s 240 Gb/s | 75 GB/s 600 Gb/s |

See also[edit]

Retrieved from "https://en.wikichip.org/w/index.php?title=cavium/ccpi&oldid=92091"