From WikiChip

Editing intel/mcs-4/4004

Warning: You are not logged in. Your IP address will be publicly visible if you make any edits. If you log in or create an account, your edits will be attributed to your username, along with other benefits.

The edit can be undone.

Please check the comparison below to verify that this is what you want to do, and then save the changes below to finish undoing the edit.

This page supports semantic in-text annotations (e.g. "[[Is specified as::World Heritage Site]]") to build structured and queryable content provided by Semantic MediaWiki. For a comprehensive description on how to use annotations or the #ask parser function, please have a look at the getting started, in-text annotation, or inline queries help pages.

| Latest revision | Your text | ||

| Line 1: | Line 1: | ||

{{intel title|4004}} | {{intel title|4004}} | ||

| − | {{ | + | {{mpu |

| − | |name=4004 | + | | name = Intel 4004 |

| − | |image= | + | | image = C4004 (Intel).jpg |

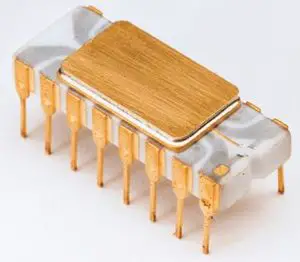

| − | |caption=4004 in CerDIP | + | | caption = Intel C4004, 4004 in CerDIP |

| − | + | | manufacturer = Intel | |

| − | |manufacturer=Intel | + | | model number = 4004 |

| − | |model number=4004 | + | | first announced = November 15, 1971 |

| − | + | | first launched = December, 1971 | |

| − | + | | last order = 1982 | |

| − | + | | family = MCS-4 | |

| − | + | | frequency = 500 kHz | |

| − | + | | frequency 2 = 740 kHz | |

| − | |first announced=November 15, 1971 | + | | microarch = 4004 |

| − | |first launched=December, 1971 | + | | process = 10 μm |

| − | |last order=1982 | + | | transistors = 2,300 |

| − | |family=MCS-4 | + | | technology = pMOS |

| − | + | | die size = | |

| − | |frequency=500 kHz | + | | word size = 4 bit |

| − | |frequency 2=740 kHz | + | | max memory addr = 4 kB |

| − | + | | electrical = Yes | |

| − | + | | power = 1 W | |

| − | |microarch=4004 | + | | temp max = 70 °C |

| − | + | | temp min = 0 °C | |

| − | + | | packaging = Yes | |

| − | + | | package = CerDIP16 | |

| − | |process=10 | + | | package type = CerDIP |

| − | |transistors=2, | + | | package 1 = DIP16 |

| − | |technology=pMOS | + | | package type 1 = DIP |

| − | |die | ||

| − | |||

| − | |||

| − | |word size=4 bit | ||

| − | |||

| − | |||

| − | |max memory addr=4 kB | ||

| − | |power=1 W | ||

| − | | | ||

| − | |||

| − | |||

| − | |||

| − | | | ||

| − | |||

| − | |packaging=Yes | ||

| − | |package | ||

| − | |package | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |package 1= | ||

| − | |package 1 | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

}} | }} | ||

| − | The '''Intel 4004''' was released by [[Intel Corporation]] in [[1971]] and was the first commercially available [[microprocessor]]. The 4004 was a [[4-bit architecture|4-bit CPU]], designed for use in the [[Busicom]] 141-PF printing calculator<ref>[http://www.intel.com/content/www/us/en/history/museum-story-of-intel-4004.html The Story of the Intel® 4004]</ref>. The chip, which is clocked at 740 KHz, employs a 10µm<ref>[ | + | The '''Intel 4004''' was released by [[Intel Corporation]] in [[1971]] and was the first commercially available [[microprocessor]]. The 4004 was a [[4-bit architecture|4-bit CPU]], designed for use in the [[Busicom]] 141-PF printing calculator<ref>[http://www.intel.com/content/www/us/en/history/museum-story-of-intel-4004.html The Story of the Intel® 4004]</ref>. The chip, which is clocked at 740 KHz, employs a 10µm<ref>[http://www.intel.com/Assets/PDF/DataSheet/4004_datasheet.pdf 4004 Datasheet]</ref> process silicon-gate, capable of executing 92,000 instructions per second. The chip was capable of accessing 4KB of [[program memory]] and 640 bytes of RAM. The 4004 was part of the [[Intel MCS-4]] system. |

The microprocessor had a limited architecture, such as: only a 3-levels deep [[stack]], a complex memory access scheme, and no [[interrupt]] support. In [[1974]] Intel released an enhanced version of the chip called the [[Intel 4040|4040]]. | The microprocessor had a limited architecture, such as: only a 3-levels deep [[stack]], a complex memory access scheme, and no [[interrupt]] support. In [[1974]] Intel released an enhanced version of the chip called the [[Intel 4040|4040]]. | ||

| Line 66: | Line 37: | ||

Three primary source variations were produced by Intel: C4004, D4004 and the P4004. The ''Intel C4004'' was the first chip to be manufactured; it had the gray traces visible on the white ceramic package itself. The C4004 was produced up until mid 1976, when production for the ''Intel D4004'' began. The D4004 had a plastic, black ceramic package. The ''Intel P4004'' is the plastic packaging version. | Three primary source variations were produced by Intel: C4004, D4004 and the P4004. The ''Intel C4004'' was the first chip to be manufactured; it had the gray traces visible on the white ceramic package itself. The C4004 was produced up until mid 1976, when production for the ''Intel D4004'' began. The D4004 had a plastic, black ceramic package. The ''Intel P4004'' is the plastic packaging version. | ||

| − | A couple | + | A couple secondary sources exists, which has been developed by National Semiconductor and Hitachi since mid-1975. National Semiconductor produced two versions: ''INS4004J'' and ''INS4004D''. The ''INS4004J'' is a 16-pin black, ceramic DIP, while the ''INS4004D'' version is a 16-pin side-brazed, ceramic DIP. The other source was the {{hitachi|HD35404}} made by [[Hitachi]]. A third source was [[Microsystems International]] which actually manufactured an enhanced version of the chip since mid 1970 (also introduced in 1971). |

{| class="wikitable" | {| class="wikitable" | ||

| Line 112: | Line 83: | ||

| 7 || Clock Phase 2 | | 7 || Clock Phase 2 | ||

|- | |- | ||

| − | | 8 || Sync || ROM & RAM Sync || Synchronizes the ROM and RAM by signaling the clock is on the | + | | 8 || Sync || ROM & RAM Sync || Synchronizes the ROM and RAM by signaling the clock is on the raising edge. |

|- | |- | ||

| 9 || Reset || Reset flag || A logic 1 clears all processor status registers and forces the program counter to jump to address 0x0. The RESET signal must be on for at least 64 clock cycles in order to take effect. | | 9 || Reset || Reset flag || A logic 1 clears all processor status registers and forces the program counter to jump to address 0x0. The RESET signal must be on for at least 64 clock cycles in order to take effect. | ||

| Line 122: | Line 93: | ||

| 12 || V<sub>DD</sub> || V<sub>SS</sub> -15±5% || | | 12 || V<sub>DD</sub> || V<sub>SS</sub> -15±5% || | ||

|- | |- | ||

| − | | 13 || CM-RAM<sub>3</sub> || rowspan="4" | CM- | + | | 13 || CM-RAM<sub>3</sub> || rowspan="4" | CM-ROM outputs || rowspan="4" | Bank selection signal for the [[Intel 4002|4002 RAM]] chips in the system. |

|- | |- | ||

| 14 || CM-RAM<sub>2</sub> | | 14 || CM-RAM<sub>2</sub> | ||

| Line 137: | Line 108: | ||

* [[designer::Stan Mazor]] | * [[designer::Stan Mazor]] | ||

* [[designer::Masatoshi Shim]] | * [[designer::Masatoshi Shim]] | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

== References == | == References == | ||

{{reflist}} | {{reflist}} | ||

| + | |||

| + | {{DEFAULTSORT:4004}} | ||

Facts about "4004 - Intel"

| base frequency | 0.5 MHz (5.0e-4 GHz, 500 kHz) + and 0.74 MHz (7.4e-4 GHz, 740 kHz) + |

| chipset | 4001 +, 4002 + and 4003 + |

| core count | 1 + |

| core voltage | 15 V (150 dV, 1,500 cV, 15,000 mV) + |

| core voltage tolerance | 5% + |

| designer | Ted Hoff +, Federico Faggin +, Stan Mazor +, Intel + and Masatoshi Shim + |

| die area | 12 mm² (0.0186 in², 0.12 cm², 12,000,000 µm²) + |

| die length | 4 mm (0.4 cm, 0.157 in, 4,000 µm) + |

| die width | 3 mm (0.3 cm, 0.118 in, 3,000 µm) + |

| family | MCS-4 + |

| first announced | November 15, 1971 + |

| first launched | December 1971 + |

| full page name | intel/mcs-4/4004 + |

| instance of | microprocessor + |

| isa | 4004 + |

| isa family | 4004 + |

| last order | 1982 + |

| ldate | December 1971 + |

| main image |  + + |

| main image caption | 4004 in CerDIP + |

| manufacturer | Intel + |

| market segment | Commercial + and Industrial + |

| max ambient temperature | 343.15 K (70 °C, 158 °F, 617.67 °R) + |

| max memory address | 4 kB + |

| max storage temperature | 398.15 K (125 °C, 257 °F, 716.67 °R) + |

| microarchitecture | 4004 + |

| min ambient temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| min storage temperature | 218.15 K (-55 °C, -67 °F, 392.67 °R) + |

| model number | 4004 + |

| name | 4004 + |

| part number | C4004 +, P4004 + and D4004 + |

| power dissipation | 1 W (1,000 mW, 0.00134 hp, 0.001 kW) + |

| process | 10,000 nm (10 μm, 0.01 mm) + |

| series | MCS + |

| technology | pMOS + |

| thread count | 1 + |

| transistor count | 2,250 + |

| word size | 4 bit (0.5 octets, 1 nibbles) + |