The Frequency Behavior of Intel's CPUs is complex and is governed by multiple mechanisms that perform dynamic frequency scaling based on the available headroom.

Contents

Overview

With the increasing transistor budget new features are added and the overall core grows in capabilities. Unfortunately, the power constraints have remained the same and in many situations have gotten more restrictive. The result is that despite the exponentially increasing density, the dark silicon's area is growing just as fast.

Intel has implemented a number of mechanisms into their architectures to extract additional performance through higher frequency whenever the power and thermal budgets allow.

- Intelligent Power Capability

- Enhanced Intel SpeedStep Technology (EIST) - Introduced with Pentium M, 2005

- Dynamic Acceleration Technology (DAT) - Introduced with Modified Pentium M/Core 2006

- Turbo Boost Technology (TBT) - Introduced with Nehalem in 2008

- Turbo Boost Technology 2.0 (TBT 2.0) - Introduced with Sandy Bridge in 2010

- Speed Shift Technology (SST) - Introduced with Skylake in 2015

- Turbo Boost Max Technology 3.0 (TBMT) - Introduced with Broadwell E in 2016

Base, LFM, HFM

| Example P-State Table | |

|---|---|

| Voltage | Frequency |

| 1.21 V | 2.8 GHz (HFM) |

| 1.18 V | 2.4 GHz |

| 1.05 V | 2.0 GHz |

| 0.96 V | 1.6 GHz |

| 0.93 V | 1.3 GHz |

| 0.86 V | 900 MHz |

| 0.80 V | 600 MHz (LFM) |

With EIST, which is found on pretty much every Intel's processor since the mid-2000, each processor comes with a series of frequencies and associated voltages (note that a tuple containing the voltage and frequency is called a P-State). An example frequency table is shown on the left. This table is stored within the read-only processor model specific register (MSR) and is used to ensure that frequencies do not exceed the lower or upper bound. The lower bound is called the Low Frequency Mode (LFM) and is the lowest frequency-voltage operating point for a given processor. The upper bound is called the High Frequency mode (HFM) and is the highest frequency-voltage operating point. Note that the HFM frequency is usually referred to by its advertised name: Base Frequency.

Most of the time, the processor does very little work. In order to save power, the processor will drop into a lower P-State when not under any demanding workloads. The processor will switch around between the various P-States as needed and as dictated by the operating system.

Base, Non-AVX Turbo, and AVX Turbo

Because different workloads exhibit different die thermos and electrical characteristics, they also have different frequencies. Intel organizes workloads into three categories:

- Non-AVX - workloads such as SSE and simple (e.g., add/bit) integer vector operations and all other regular instructions.

- AVX2 Heavy - workloads that make heavy use of complex AVX2 operations (e.g. floating point and integer vector multiplications). This also includes the various AVX-512 bit scanning, and other simple (i.e., non INT/FP MUL) operations.

- AVX-512 Heavy - workloads that make use of complex AVX-512 operations, including operations such as floating point and integer vector multiplications.

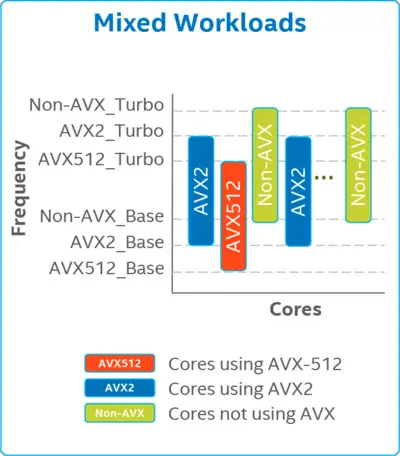

The frequency of each core is determined independently based on the workload described above. That is, cores running Non-AVX workloads can enjoy the full regular turbo frequency, whereas cores executing AVX-512 or AVX2 will operate at their own designated turbo frequencies.

Due to all of that, each processor has the following properties:

| Mode | Example Workload | Absolute Guaranteed Lowest Frequency |

Absolute Highest Frequency |

|---|---|---|---|

| Non-AVX | SSE, light AVX2 Integer Vector (non-MUL), All regular instruction | Base Frequency | Turbo Frequency |

| AVX2 Heavy | All AVX2 operations, light AVX-512 (non-FP, Int Vect non-MUL) | AVX2 Base | AVX2 Turbo |

| AVX-512 Heavy | All heavy AVX-512 operations | AVX-512 Base | AVX-512 Turbo |

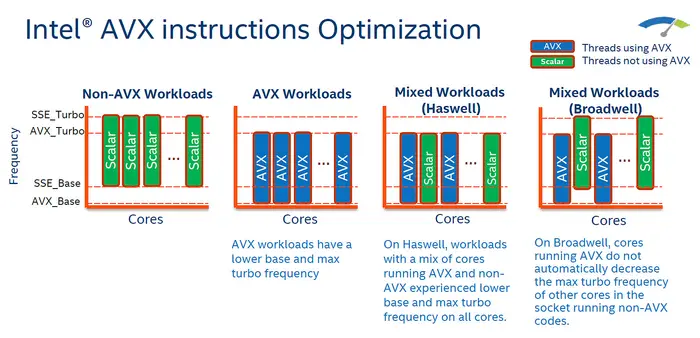

Historical behavior

In Haswell, an AVX2 workload on one core meant all cores were capped at AVX2 Turbo frequency. This had the undesirable effect of reducing performance for non-AVX workloads on cores that were unrelated to the cores executing AVX2 workloads. This behavior was changed with Broadwell which grouped cores executing AVX2 workloads together and cores executing non-AVX workloads separately, allowing the former cores group to execute at the lower AVX2 turbo frequency while having the later cores group execute at full non-AVX2 turbo.

See also

- AMD's Frequency Behavior