From WikiChip

R-Car E1 - Renesas

| Edit Values | |||||||||||

| R-Car E1 | |||||||||||

| |||||||||||

| General Info | |||||||||||

| Designer | Renesas, ARM Holdings | ||||||||||

| Manufacturer | TSMC | ||||||||||

| Model Number | E1 | ||||||||||

| Part Number | μPD35004 | ||||||||||

| Market | Embedded | ||||||||||

| Introduction | August 25, 2011 (announced) June, 2012 (launched) | ||||||||||

| Release Price | $30 | ||||||||||

| General Specs | |||||||||||

| Family | R-Car | ||||||||||

| Series | 1st Gen | ||||||||||

| Frequency | 533 MHz | ||||||||||

| Microarchitecture | |||||||||||

| ISA | ARMv7 (ARM) | ||||||||||

| Microarchitecture | Cortex-A9 | ||||||||||

| Core Name | Cortex-A9 | ||||||||||

| Process | 40 nm | ||||||||||

| Technology | CMOS | ||||||||||

| Word Size | 32 bit | ||||||||||

| Cores | 1 | ||||||||||

| Threads | 1 | ||||||||||

| Max Memory | 1 GiB | ||||||||||

| Multiprocessing | |||||||||||

| Max SMP | 1-Way (Uniprocessor) | ||||||||||

| Electrical | |||||||||||

| Vcore | 1.1 V | ||||||||||

| VI/O | 3.3 V | ||||||||||

| Packaging | |||||||||||

| |||||||||||

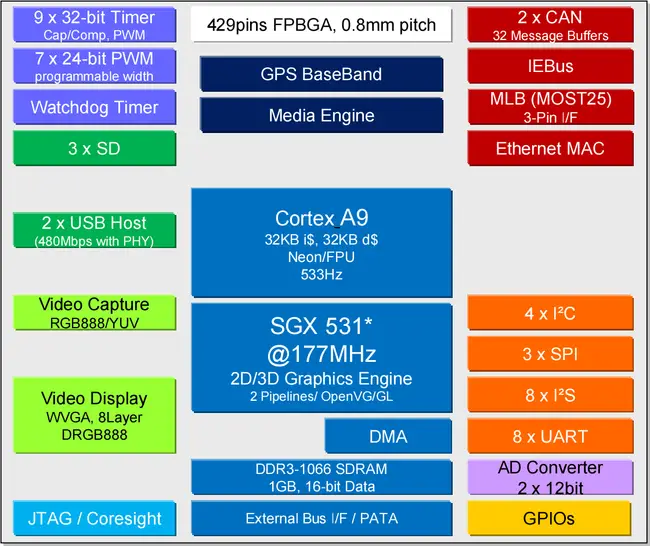

R-Car E1 is an entry-level performance embedded SoC for the automotive industry designed by Renesas and introduced in 2011. The E1 features a single Cortex-A9 core operating at 533 MHz. This chip incorporates Imagination's PowerVR SGX531 GPU operating at 177 MHz. This SoC supports up to 1 GiB of DDR3-1066 memory.

Announced in mid-2011, Renesas expected the E1 to begin mass production in June 2012 and reach a rate of 100,000 units per month in June 2013.

Cache

- Main article: Cortex-A9 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||

|

|||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Expansions

|

Expansion Options

|

||||||||||||||||||||||||||

|

||||||||||||||||||||||||||

- MLB (MOST150) 6-Pin I/F

- 2 x CAN 32 Message Buffers

- MMC

- 3 x SD

Graphics

|

Integrated Graphics Information

|

||||||||||||||||||||||

|

||||||||||||||||||||||

Features

[Edit/Modify Supported Features]

|

Supported ARM Extensions & Processor Features

|

||||||||||

|

||||||||||

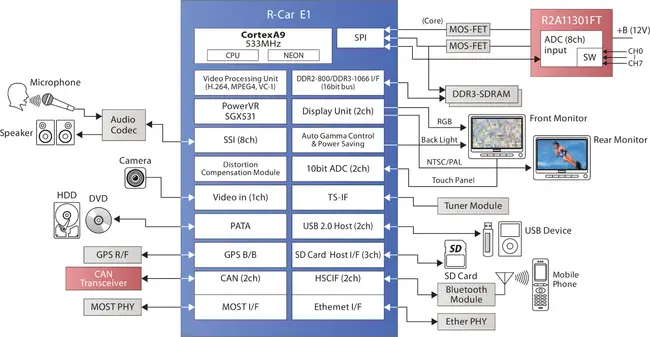

Block Diagram

Facts about "R-Car E1 - Renesas"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | R-Car E1 - Renesas#package + |

| base frequency | 533 MHz (0.533 GHz, 533,000 kHz) + |

| core count | 1 + |

| core name | Cortex-A9 + |

| core voltage | 1.1 V (11 dV, 110 cV, 1,100 mV) + |

| designer | Renesas + and ARM Holdings + |

| family | R-Car + |

| first announced | August 25, 2011 + |

| first launched | June 2012 + |

| full page name | renesas/r-car/e1 + |

| has ecc memory support | false + |

| instance of | microprocessor + |

| integrated gpu | PowerVR SGX531 + |

| integrated gpu base frequency | 177 MHz (0.177 GHz, 177,000 KHz) + |

| integrated gpu designer | Imagination Technologies + |

| integrated gpu execution units | 1 + |

| io voltage | 3.3 V (33 dV, 330 cV, 3,300 mV) + |

| isa | ARMv7 + |

| isa family | ARM + |

| l1$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1d$ description | 4-way set associative + |

| l1d$ size | 32 KiB (32,768 B, 0.0313 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 32 KiB (32,768 B, 0.0313 MiB) + |

| ldate | June 2012 + |

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Embedded + |

| max cpu count | 1 + |

| max memory | 1,024 MiB (1,048,576 KiB, 1,073,741,824 B, 1 GiB, 9.765625e-4 TiB) + |

| max memory bandwidth | 1.99 GiB/s (2,037.76 MiB/s, 2.137 GB/s, 2,136.746 MB/s, 0.00194 TiB/s, 0.00214 TB/s) + |

| max memory channels | 1 + |

| microarchitecture | Cortex-A9 + |

| model number | E1 + |

| name | R-Car E1 + |

| package | FCBGA-429 + |

| part number | μPD35004 + |

| process | 40 nm (0.04 μm, 4.0e-5 mm) + |

| release price | $ 30.00 (€ 27.00, £ 24.30, ¥ 3,099.90) + |

| series | 1st Gen + |

| smp max ways | 1 + |

| supported memory type | DDR3-1066 + and DDR2-533 + |

| technology | CMOS + |

| thread count | 1 + |

| word size | 32 bit (4 octets, 8 nibbles) + |