-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

Rosetta - Microarchitectures - Cray

| Edit Values | |

| Rosetta µarch | |

| General Info | |

| Arch Type | Switch |

| Designer | Cray |

| Manufacturer | TSMC |

| Introduction | 2019 |

| Process | 16 nm |

Rosetta is the microarchitecture for Cray's Slingshot ASIC Switch.

Process technology

| This section is empty; you can help add the missing info by editing this page. |

Overview

| This section is empty; you can help add the missing info by editing this page. |

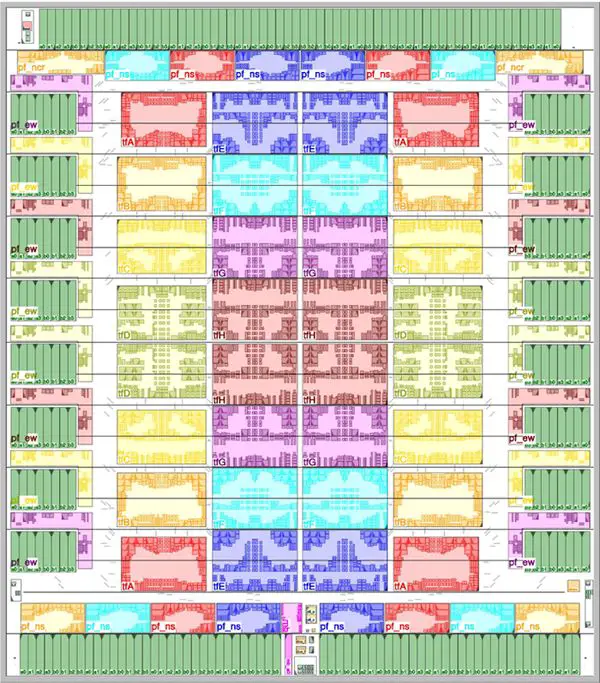

Die

- TSMC 16 nm process

- 64 port

- 250 W

- tiled architecture

- 32 tile blocks

- peripheral function blocks

floorplan:

Bibliography

- Cray, 2019 IEEE Symposium on High-Performance Interconnects (HOTI).

Retrieved from "https://en.wikichip.org/w/index.php?title=cray/microarchitectures/rosetta&oldid=95874"

Hidden category:

Facts about "Rosetta - Microarchitectures - Cray"

| codename | Rosetta + |

| designer | Cray + |

| first launched | 2019 + |

| full page name | cray/microarchitectures/rosetta + |

| instance of | microarchitecture + |

| manufacturer | TSMC + |

| name | Rosetta + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |