From WikiChip

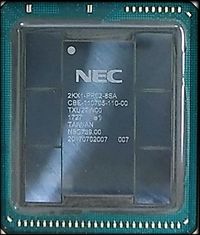

Vector Engine Type 10C - NEC

| Edit Values | |

| VE Type 10C | |

| |

| General Info | |

| Designer | NEC |

| Manufacturer | TSMC |

| Model Number | Type 10C |

| Market | Server, Workstation |

| Introduction | Oct 26, 2017 (announced) 2018 (launched) |

| General Specs | |

| Family | Vector Engine |

| Series | Type 10 |

| Frequency | 1,400 MHz |

| Microarchitecture | |

| Microarchitecture | SX-Aurora |

| Platform | SX-Aurora TSUBASA |

| Process | 16 nm |

| Transistors | 4,800,000,000 |

| Technology | CMOS |

| Die | 493.68 mm² 14.96 mm × 33.00 mm |

| Word Size | 64 bit |

| Cores | 8 |

| Threads | 8 |

| Max Memory | 24 GiB |

| Succession | |

Vector Engine Type 10C is an octa-core vector processor designed by NEC and introduced in late 2017. This chip is fabricated on TSMC 16 nm process based on the SX-Aurora mircoarchitecture. VE Type 10C operates at 1.4 GHz and comes with 24 GiB of six 4-hi stacks of HBM2 memory.

Performance[edit]

The Vector Engine Type 10C operates at 1.4 GHz and integrates eight vector cores.

- Per core: 269 gigaFLOPS

- Per chip: 2.15 teraFLOPS2,150,000,000,000 FLOPS

2,150,000,000 KFLOPS

2,150,000 MFLOPS

2,150 GFLOPS

0.00215 PFLOPS

Cache[edit]

- Main article: SX-Aurora § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Expansions[edit]

Expansion Options |

|||||

|

|||||

Card[edit]

The Vector Engine Type 10C supports air cooling and passive cooling options.

Air active cooled:

Passive cooled:

Facts about "Vector Engine Type 10C - NEC"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Vector Engine Type 10C - NEC#pcie + |

| base frequency | 1,400 MHz (1.4 GHz, 1,400,000 kHz) + |

| core count | 8 + |

| designer | NEC + |

| die area | 493.68 mm² (0.765 in², 4.937 cm², 493,680,000 µm²) + |

| die length | 14.96 mm (1.496 cm, 0.589 in, 14,960 µm) + |

| die width | 33 mm (3.3 cm, 1.299 in, 33,000 µm) + |

| family | Vector Engine + |

| first announced | October 26, 2017 + |

| first launched | 2018 + |

| full page name | nec/vector engine/type 10c + |

| has ecc memory support | false + |

| instance of | microprocessor + |

| l1$ size | 512 KiB (524,288 B, 0.5 MiB) + |

| l1d$ size | 256 KiB (262,144 B, 0.25 MiB) + |

| l1i$ size | 256 KiB (262,144 B, 0.25 MiB) + |

| l2$ size | 2 MiB (2,048 KiB, 2,097,152 B, 0.00195 GiB) + |

| l3$ size | 16 MiB (16,384 KiB, 16,777,216 B, 0.0156 GiB) + |

| ldate | 2018 + |

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Server + and Workstation + |

| max memory | 24,576 MiB (25,165,824 KiB, 25,769,803,776 B, 24 GiB, 0.0234 TiB) + |

| max memory bandwidth | 715.256 GiB/s (732,421.875 MiB/s, 768 GB/s, 768,000 MB/s, 0.698 TiB/s, 0.768 TB/s) + |

| max memory channels | 48 + |

| microarchitecture | SX-Aurora + |

| model number | Type 10C + |

| name | VE Type 10C + |

| peak flops (double-precision) | 2,150,000,000,000 FLOPS (2,150,000,000 KFLOPS, 2,150,000 MFLOPS, 2,150 GFLOPS, 2.15 TFLOPS, 0.00215 PFLOPS, 2.15e-6 EFLOPS, 2.15e-9 ZFLOPS) + |

| platform | SX-Aurora TSUBASA + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |

| series | Type 10 + |

| supported memory type | HBM2-1000 + |

| technology | CMOS + |

| thread count | 8 + |

| transistor count | 4,800,000,000 + |

| word size | 64 bit (8 octets, 16 nibbles) + |