From WikiChip

Knights Landing - Microarchitectures - Intel

| Edit Values | |

| Knights Landing µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Process | 14 nm |

| Core Configs | 64, 68, 72 |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | x86-16, x86-32, x86-64 |

| Extensions | AVX-512 |

| Cache | |

| L1I Cache | 32 kiB/core |

| L1D Cache | 32 kiB/core 8-way associate |

| L2 Cache | 1 MiB/shared between cores within tile |

| Cores | |

| Core Names | Silvermont |

| Succession | |

| Contemporary | |

| Knights Mill | |

Knights Landing (KNL) is the successor to Knights Corner, a 14 nm many-core microarchitecture designed by Intel for high performance computing.

Contents

Process Technology[edit]

- See also: Broadwell § Process Technology and 14 nm lithography process

Knights Landing is fabricated on Intel's 14 nm process.

Architecture[edit]

Key changes from Knights Corner[edit]

| This section is empty; you can help add the missing info by editing this page. |

New instructions[edit]

Knights Landing introduced a number of new instructions:

-

AVX-512, specifically:

Die[edit]

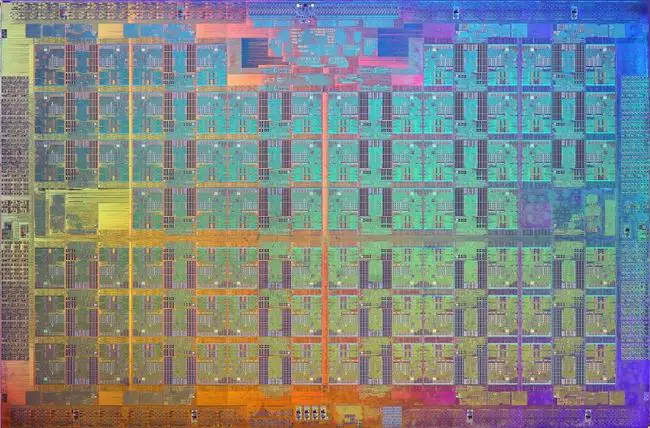

Die shot of Intel's Xeon Phi, Knights Landing.

- 14 nm process

- 682.6 mm² die size

- 76 CPU cores (sold with maximum 72 enabled cores)

- 7,100,000,000 transistors

Facts about "Knights Landing - Microarchitectures - Intel"

| codename | Knights Landing + |

| core count | 64 +, 68 + and 72 + |

| designer | Intel + |

| full page name | intel/microarchitectures/knights landing + |

| instance of | microarchitecture + |

| instruction set architecture | x86-16 +, x86-32 + and x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Knights Landing + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |