From WikiChip

QorIQ P2020 - Freescale

| Edit Values | |||||||

| P2020 | |||||||

| General Info | |||||||

| Designer | Freescale | ||||||

| Manufacturer | IBM | ||||||

| Model Number | P2010 | ||||||

| Market | Networking, Embedded | ||||||

| Introduction | June 16, 2008 (announced) 2009 (launched) | ||||||

| General Specs | |||||||

| Family | QorIQ | ||||||

| Series | P2 | ||||||

| Frequency | 1,200 MHz | ||||||

| Microarchitecture | |||||||

| ISA | Power ISA v2.03 (Power) | ||||||

| Microarchitecture | e500 | ||||||

| Core Name | e500 | ||||||

| Process | 45 nm | ||||||

| Technology | CMOS | ||||||

| Word Size | 32 bit | ||||||

| Cores | 2 | ||||||

| Threads | 2 | ||||||

| Electrical | |||||||

| Power dissipation | 8 W | ||||||

| Tjunction | 0 °C – 125 °C | ||||||

| Packaging | |||||||

| |||||||

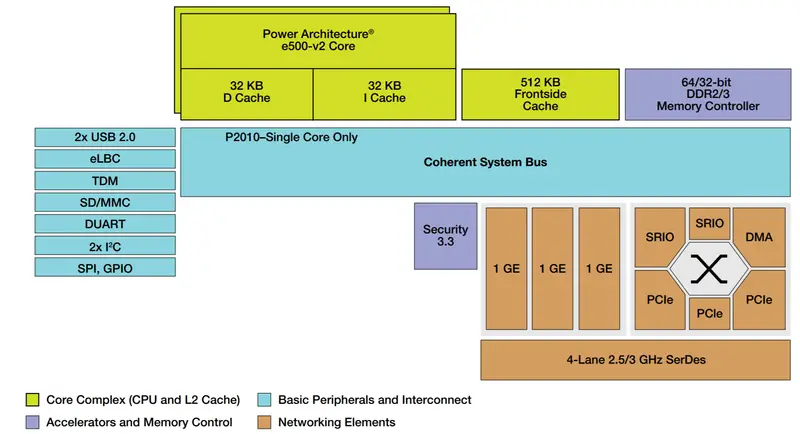

QorIQ P2020 is a 32-bit embedded dual-core POWER microprocessor introduced by Freescale in 2008. This networking/embedded processor, which is based on the e500 microarchitecture and is fabricated on a 45 nm SOI process, operates at 1.2 GHz and supports 64-bit DDR3-800 memory.

Cache

- Main article: e500 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions

- 3x 10/100/1000 Eithernet with SGMII

- 3x PCIe 1.0a controllers with 2 SerDes

- 1x USB 2.0

- SD/MMC

- SPI

- 2x I2C

- UART

- SEC 3.1 Security Acceleration

Block Diagram

Documents

Facts about "QorIQ P2020 - Freescale"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | QorIQ P2020 - Freescale#package + |

| base frequency | 1,200 MHz (1.2 GHz, 1,200,000 kHz) + |

| core count | 2 + |

| core name | e500 + |

| designer | Freescale + |

| family | QorIQ + |

| first announced | June 16, 2008 + |

| first launched | 2009 + |

| full page name | freescale/qoriq/p2020 + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| isa | Power ISA v2.03 + |

| isa family | Power + |

| l1$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| ldate | 2009 + |

| manufacturer | IBM + |

| market segment | Networking + and Embedded + |

| max junction temperature | 398.15 K (125 °C, 257 °F, 716.67 °R) + |

| max memory bandwidth | 5.96 GiB/s (6,103.04 MiB/s, 6.4 GB/s, 6,399.501 MB/s, 0.00582 TiB/s, 0.0064 TB/s) + |

| max memory channels | 1 + |

| microarchitecture | e500 + |

| min junction temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| model number | P2010 + |

| name | P2020 + |

| package | TE-PBGA-II-689 + |

| power dissipation | 8 W (8,000 mW, 0.0107 hp, 0.008 kW) + |

| process | 45 nm (0.045 μm, 4.5e-5 mm) + |

| series | P2 + |

| supported memory type | DDR3-800 + |

| technology | CMOS + |

| thread count | 2 + |

| word size | 32 bit (4 octets, 8 nibbles) + |