Template:mpu Atom Z612 is an ultra-low power 32-bit x86 system on a chip designed by Intel and introduced in early 2010. The Z612, which is based on the Bonnell microarchitecture (Lincroft core), is fabricated on a 45 nm process. This SoC incorporates a single core operating at 900 MHz with a low frequency mode of 600 MHz and a burst frequency of 1.5 GHz. The chip has a TDP of 1.3 W and supporting up to a 2 GiB of single-channel DDR2-800 memory. Additionally, the Z612 incorporates a GMA 600 IGP operating at 400 MHz.

This chip communicates with the southbridge chipset (PCH MP30) over two buses: cDMI and cDVO. Both buses go from the SoC to the chipset. cDMI, which is used as the data interface link, operates at 100 MHz using a quad-pumped rate (i.e. 400 MT/s). That bus is composed of an 8-bit transmit and 8-bit receive. The cDVO, which is used as a unidirectional display data link is a quad-pumped 6-bit bus operating 100 MHz for a 400 MT/s effective rate. This model uses CMOS signaling for both buses.

Cache

- Main article: Bonnell § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||||||

|

||||||||||||||||||

Expansions

|

Expansion Options

|

||||||||||

|

||||||||||

Graphics

This chip incroporates the "GMA 600" integrated graphics which is actually a re-branded licensed Imagination PowerVR SGX 535 IGP.

|

Integrated Graphics Information

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||

- Supports hardware-accelerated HD video decode (MPEG4 part 2, H.264, WMV, and VC1)

- Supports hardware-accelerated HD video encode (MPEG4 part 2 and H.264)

Features

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||

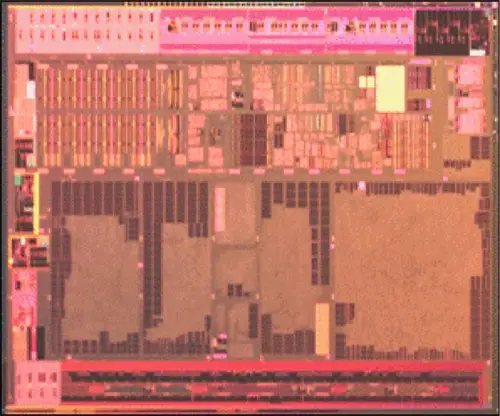

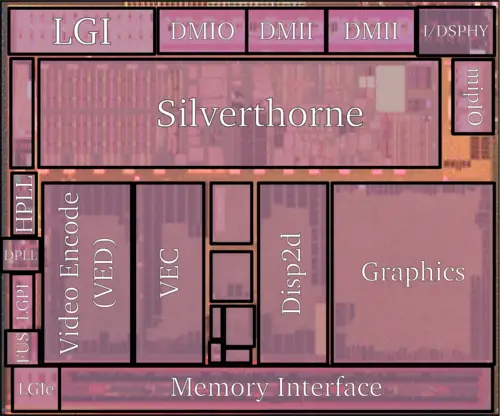

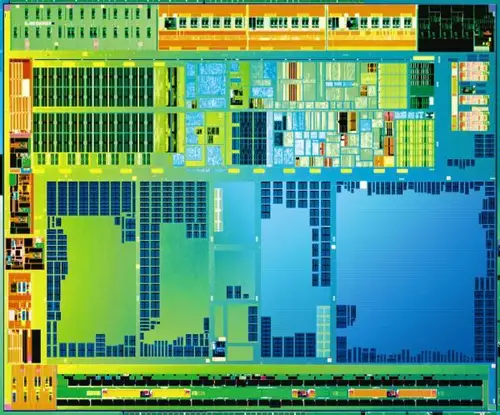

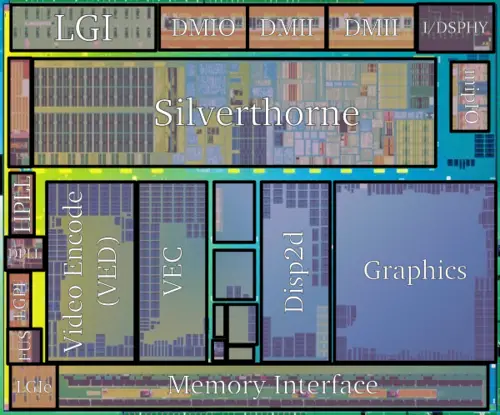

Die Shot

- See also: Bonnell § Lincroft Die

- 45 nm process

- 140,000,000

- Die size 7.34 mm × 8.89 mm

- Size area 65.2526 mm²

| has ecc memory support | false + |

| has feature | Hyper-Threading Technology +, Burst Performance Technology + and Enhanced SpeedStep Technology + |

| has intel burst performance technology | true + |

| has intel enhanced speedstep technology | true + |

| has simultaneous multithreading | true + |

| integrated gpu | PowerVR SGX535 + |

| integrated gpu base frequency | 200 MHz (0.2 GHz, 200,000 KHz) + |

| integrated gpu designer | Imagination Technologies + |

| integrated gpu max memory | 256 MiB (262,144 KiB, 268,435,456 B, 0.25 GiB) + |

| l1$ size | 56 KiB (57,344 B, 0.0547 MiB) + |

| l1d$ description | 6-way set associative + |

| l1d$ size | 24 KiB (24,576 B, 0.0234 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 32 KiB (32,768 B, 0.0313 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| max memory bandwidth | 2.98 GiB/s (3,051.52 MiB/s, 3.2 GB/s, 3,199.751 MB/s, 0.00291 TiB/s, 0.0032 TB/s) + |

| max memory channels | 1 + |

| supported memory type | DDR-400 + and DDR2-800 + |