From WikiChip

Ryzen 5 3550H - AMD

| Edit Values | |

| Ryzen 5 3550H | |

| General Info | |

| Designer | AMD |

| Manufacturer | GlobalFoundries |

| Model Number | 3550H |

| Part Number | YM3500C4T4MFG |

| Market | Mobile |

| Introduction | January 6, 2019 (announced) January 6, 2019 (launched) |

| Shop | Amazon |

| General Specs | |

| Family | Ryzen 5 |

| Series | 3000 |

| Frequency | 2,100 MHz |

| Turbo Frequency | 3,700 MHz |

| Bus type | PCIe 3.0 |

| Clock multiplier | 21 |

| Microarchitecture | |

| ISA | x86-64 (x86) |

| Microarchitecture | Zen+ |

| Core Name | Picasso |

| Process | 12 nm |

| Transistors | 4,940,000,000 |

| Technology | CMOS |

| Die | 209.78 mm² |

| Word Size | 64 bit |

| Cores | 4 |

| Threads | 8 |

| Max Memory | 64 GiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| TDP | 35 W |

| OP Temperature | 0° C – 105 °C |

| Packaging | |

| Unknown package "amd,socket_fp5" | |

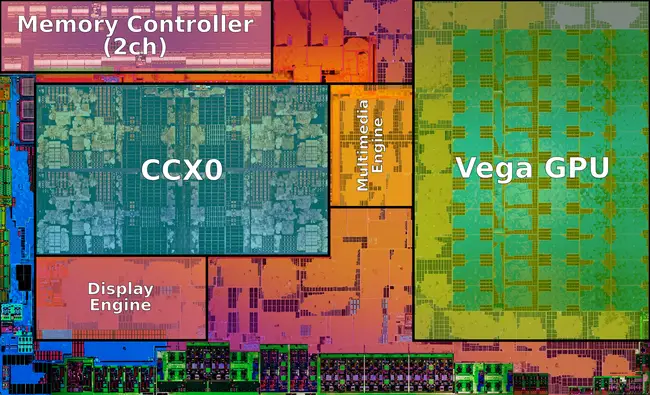

Ryzen 5 3550H is a 64-bit quad-core mid-range performance x86 mobile microprocessor introduced by AMD in early 2019. This processor is based on AMD's Zen+ microarchitecture and is fabricated on a 12 nm process. The 3550H operates at a base frequency of 2.1 GHz with a TDP of 35 W and a Boost frequency of 3.7 GHz. This APU supports up to 32 GiB of dual-channel DDR4-2400 memory and incorporates Radeon Vega 8 Graphics operating at up to 1.2 GHz.

Cache

- Main article: Zen+ § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions

This processor has 12 PCIe lanes, 1x8 typically designated for a GPU and 4 additional lanes for storage (e.g., NVMe).

Expansion Options |

|||||

|

|||||

Graphics

|

Integrated Graphics Information

|

||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||

| [Edit] Zen with Radeon Vega Hardware Accelerated Video Capabilities | |||||

|---|---|---|---|---|---|

| Codec | Encode | Decode | |||

| Max FPS | @1080p | @1440p | @2160p | @1080p 4:2:0 | @2160p 4:2:0 |

| MPEG-2 (H.262) | 60 FPS | N/A | |||

| VC-1 | |||||

| VP9 8bpc | 240 FPS | 60 FPS | |||

| VP9 10bpc | |||||

| MPEG-4 AVC (H.264) 8bpc | 120 FPS | 60 FPS | 30 FPS | ||

| MPEG-4 AVC (H.264) 10bpc | |||||

| HEVC (H.265) 8bpc | 120 FPS | 60 FPS | 30 FPS | ||

| HEVC (H.265) 10bpc | |||||

| JPEG/MJPEG 8bpc | |||||

Features

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Die

- Further information: Zen+ § Die

- 14 nm process

- 4,940,000,000 transistors

- 209.78 mm² die size

Facts about "Ryzen 5 3550H - AMD"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Ryzen 5 3550H - AMD#pcie + |

| base frequency | 2,100 MHz (2.1 GHz, 2,100,000 kHz) + |

| bus type | PCIe 3.0 + |

| clock multiplier | 21 + |

| core count | 4 + |

| core name | Picasso + |

| designer | AMD + |

| die area | 209.78 mm² (0.325 in², 2.098 cm², 209,780,000 µm²) + |

| family | Ryzen 5 + |

| first announced | January 6, 2019 + |

| first launched | January 6, 2019 + |

| full page name | amd/ryzen 5/3550h + |

| has advanced vector extensions | true + |

| has advanced vector extensions 2 | true + |

| has amd amd-v technology | true + |

| has amd amd-vi technology | true + |

| has amd sensemi technology | true + |

| has ecc memory support | true + |

| has feature | Advanced Vector Extensions +, Advanced Vector Extensions 2 +, Advanced Encryption Standard Instruction Set Extension + and SenseMI Technology + |

| has simultaneous multithreading | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| instance of | microprocessor + |

| integrated gpu | radeon vega 8 + |

| integrated gpu designer | AMD + |

| integrated gpu execution units | 8 + |

| integrated gpu max frequency | 1,200 MHz (1.2 GHz, 1,200,000 KHz) + |

| isa | x86-64 + |

| isa family | x86 + |

| l1$ size | 384 KiB (393,216 B, 0.375 MiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 256 KiB (262,144 B, 0.25 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 2 MiB (2,048 KiB, 2,097,152 B, 0.00195 GiB) + |

| l3$ size | 4 MiB (4,096 KiB, 4,194,304 B, 0.00391 GiB) + |

| ldate | January 6, 2019 + |

| manufacturer | GlobalFoundries + |

| market segment | Mobile + |

| max cpu count | 1 + |

| max memory | 65,536 MiB (67,108,864 KiB, 68,719,476,736 B, 64 GiB, 0.0625 TiB) + |

| max memory bandwidth | 35.763 GiB/s (36,621.094 MiB/s, 38.4 GB/s, 38,400 MB/s, 0.0349 TiB/s, 0.0384 TB/s) + |

| max memory channels | 2 + |

| max operating temperature | 105 °C + |

| microarchitecture | Zen+ + |

| min operating temperature | 0° C + |

| model number | 3550H + |

| name | Ryzen 5 3550H + |

| package | BGA-1140 + |

| part number | YM3500C4T4MFG + |

| process | 12 nm (0.012 μm, 1.2e-5 mm) + |

| series | 3000 + |

| smp max ways | 1 + |

| supported memory type | DDR4-2400 + |

| tdp | 35 W (35,000 mW, 0.0469 hp, 0.035 kW) + |

| technology | CMOS + |

| thread count | 8 + |

| transistor count | 4,940,000,000 + |

| turbo frequency | 3,700 MHz (3.7 GHz, 3,700,000 kHz) + |

| word size | 64 bit (8 octets, 16 nibbles) + |