From WikiChip

Mars I - Microarchitectures - Phytium

| Edit Values | |

| Mars I µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Phytium |

| Manufacturer | TSMC |

| Introduction | 2017 |

| Process | 28 nm |

| Core Configs | 64 |

| Pipeline | |

| Type | Superscalar, Pipelined |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | ARMv8 |

| Succession | |

Mars I is the first many-core ARM SoC microarchitecture designed by Phytium Technology for the Chinese server market.

Contents

Process technology

Mars I is designed for TSMC's 28 nm process.

Architecture

- 64 ARM cores

- 28 nm process

- 2 GHz

- FTC-661/0 Xiaomi core

- System memory

- DDR3

- 1600 MT/s

This list is incomplete; you can help by expanding it.

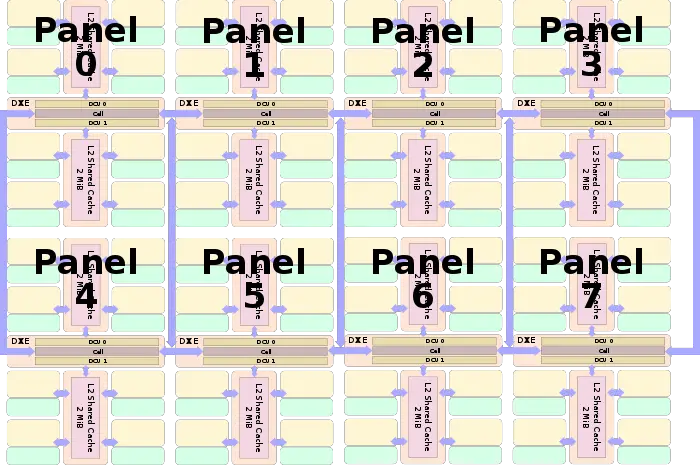

Block diagram

Entire SoC

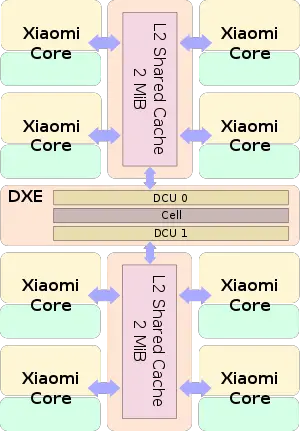

Panel

Core

- Main article: Xiaomi Core

See Xiaomi Core.

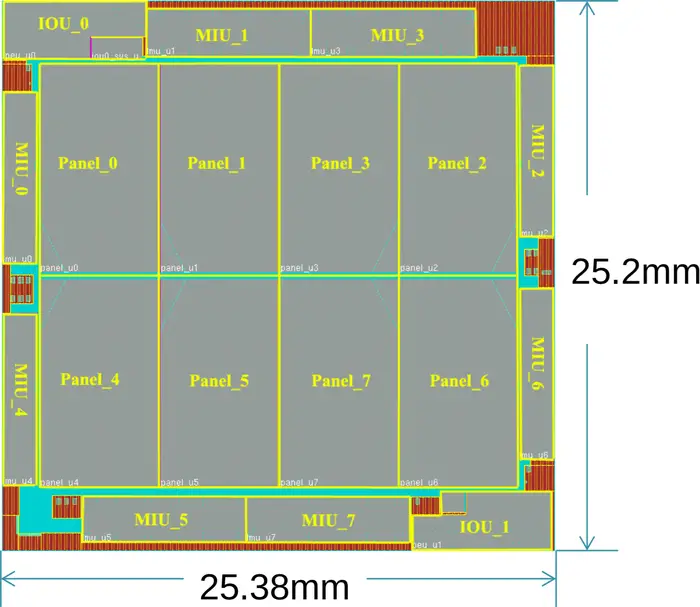

Die

SoC

- Mars is fabricated on TSMC's 28 nm process

- 10 metal layers

- ~180 million instances

- 639.576 mm² die size

- FCBGA Package

- ~3000 pins

- 0.9 VCORE, 1.8 VIO

- 2 GHz, 120 W

Facts about "Mars I - Microarchitectures - Phytium"

| codename | Mars I + |

| core count | 64 + |

| designer | Phytium + |

| first launched | 2017 + |

| full page name | phytium/microarchitectures/mars i + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Mars I + |

| process | 28 nm (0.028 μm, 2.8e-5 mm) + |