From WikiChip

AWS Graviton2 - Annapurna Labs (Amazon)

| Edit Values | |

| AWS Graviton2 | |

| |

| |

| General Info | |

| Designer | Annapurna Labs |

| Manufacturer | TSMC |

| Model Number | ALC12B00 |

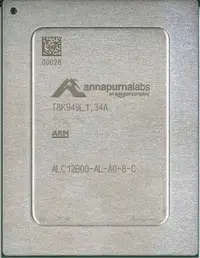

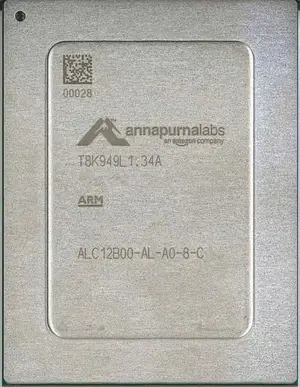

| Part Number | ALC12B00-AL-A0 |

| Market | Server |

| Introduction | December 3, 2019 (announced) December 3, 2019 (launched) |

| General Specs | |

| Family | Alpine |

| Frequency | 2,500 MHz |

| Microarchitecture | |

| ISA | ARMv8 (ARM) |

| Microarchitecture | Neoverse N1 |

| Core Name | Neoverse N1 |

| Process | 7nm |

| Transistors | 30,000,000,000 |

| Technology | CMOS |

| Die | 456.96 mm² 22.4 mm × 20.4 mm |

| Word Size | 64 bit |

| Cores | 64 |

| Threads | 64 |

| Succession | |

AWS Graviton2 (Alpine ALC12B00) is a 64-core ARMv8 SoC designed by Amazon (Annapurna Labs) for Amazon's own infrastructure, serving as a successor to the original AWS Graviton. The chip was first unveiled during Amazon's AWS re:Invent 2019 and has been in deployment for user access since early 2020. These processors are offered as part of Amazon's EC2 M6g, C6g, and R6g instances. The Graviton 2 features 64 Neoverse N1 on a mesh, all operating at 2.5 GHz.

Contents

Cache

- Main article: Neoverse N1 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||

|

||||||||||||

Expansions

|

Expansion Options

|

||||||||

|

||||||||

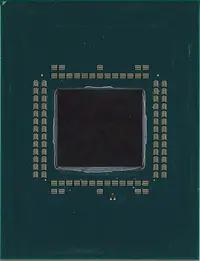

Die

- 7 nm process

- 30,000,000,000 transistors

- ~Die size

- ~456.96 mm²

- ~22.4 mm x ~20.4 mm

Facts about "AWS Graviton2 - Annapurna Labs (Amazon)"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | AWS Graviton2 - Annapurna Labs (Amazon)#io + |

| base frequency | 2,500 MHz (2.5 GHz, 2,500,000 kHz) + |

| core count | 64 + |

| core name | Neoverse N1 + |

| designer | Annapurna Labs + |

| die area | 456.96 mm² (0.708 in², 4.57 cm², 456,960,000 µm²) + |

| die length | 22.4 mm (2.24 cm, 0.882 in, 22,400 µm) + |

| die width | 20.4 mm (2.04 cm, 0.803 in, 20,400 µm) + |

| family | Graviton + |

| first announced | December 3, 2019 + |

| first launched | December 3, 2019 + |

| full page name | annapurna labs/graviton/graviton2 + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| isa | ARMv8.2-A + |

| isa family | ARM + |

| l1$ size | 8,192 KiB (8,388,608 B, 8 MiB) + |

| l1d$ size | 4,096 KiB (4,194,304 B, 4 MiB) + |

| l1i$ size | 4,096 KiB (4,194,304 B, 4 MiB) + |

| l2$ size | 64 MiB (65,536 KiB, 67,108,864 B, 0.0625 GiB) + |

| l3$ size | 32 MiB (32,768 KiB, 33,554,432 B, 0.0313 GiB) + |

| ldate | December 3, 2019 + |

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Server + |

| max memory bandwidth | 190.735 GiB/s (195,312.5 MiB/s, 204.8 GB/s, 204,800 MB/s, 0.186 TiB/s, 0.205 TB/s) + |

| max memory channels | 8 + |

| max pcie lanes | 64 + |

| microarchitecture | Neoverse N1 + |

| model number | ALC12B00 + |

| name | AWS Graviton2 + |

| part number | ALC12B00-AL-A0 + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + |

| supported memory type | DDR4-3200 + |

| technology | CMOS + |

| thread count | 64 + |

| transistor count | 30,000,000,000 + |

| word size | 64 bit (8 octets, 16 nibbles) + |