-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

amd/cores/rome

< amd

Retrieved from "https://en.wikichip.org/w/index.php?title=amd/cores/rome&oldid=96023"

Facts about "Rome - Cores - AMD"

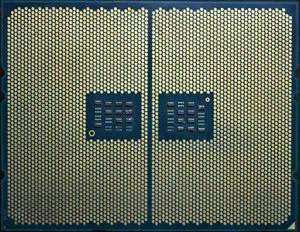

| back image |  + + |

| designer | AMD + |

| first announced | May 16, 2017 + |

| first launched | August 7, 2019 + |

| instance of | core + |

| isa | x86-64 + |

| isa family | x86 + |

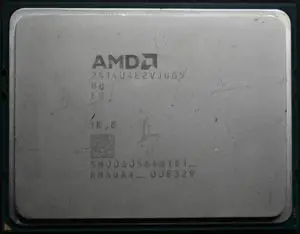

| main image |  + + |

| main image caption | Package front + |

| manufacturer | TSMC + and GlobalFoundries + |

| microarchitecture | Zen 2 + |

| name | Rome + |

| package | FCLGA-4094 + and SP3 + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + and 14 nm (0.014 μm, 1.4e-5 mm) + |

| socket | LGA-4094 + and SP3 + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |