Template:mpu PEZY-SC (PEZY Super Computer) is second generation many-core microprocessor developed by PEZY in 2014. PEZY-SC contains 2 ARM926 cores (ARMv5TEJ) along with 1,024 simpler cores supporting 8-way SMT for a total of 8,192 threads. Operating at 733 MHz, the processor has a peak performance of 3.0 TFLOPS (single-precision) and 1.5 TFLOPS (double-precision). PEZY-SC was designed using 580 million gates and manufactured on TSMC's 28HPC+. The PEZY-SC is used in a number of TOP500 & Green500 supercomputers as the world's most efficient supercomputers.

Contents

Overview

- See also: PEZY-1

The PEZY-SC (SC for "Super Computer") is PEZY's second generation microprocessors which builds upon the PEZY-1. The chip contains exactly twice as many cores and incorporates a large amount of cache including 8 MB of L3$.

In June of 2015, PEZY-SC-based supercomputers took all top 3 spots on the Green500 listing as the 3 most efficient supercomputers. PEZY-SC powers Shoubu (1,181,952 cores, ? kW, 605.624 TFlop/s Linpack Rmax), and Suiren Blue (262,656 cores, 40.86 kW, 247.752 TFlop/s Linpack Rmax), and Suiren (328,480 cores, 48.90 kW, 271.782 TFlop/s Linpack Rmax) supercomputers (ranked 1, 2, and 3 respectively).

Architecture

- Further information: PEZY-SCx § Architecture

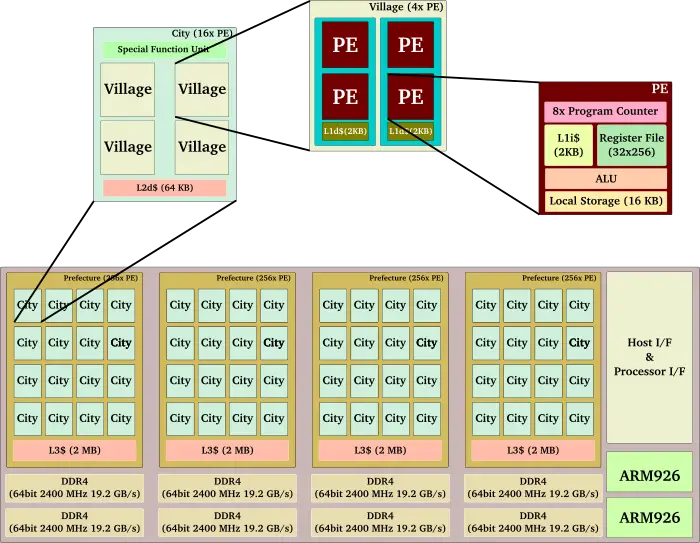

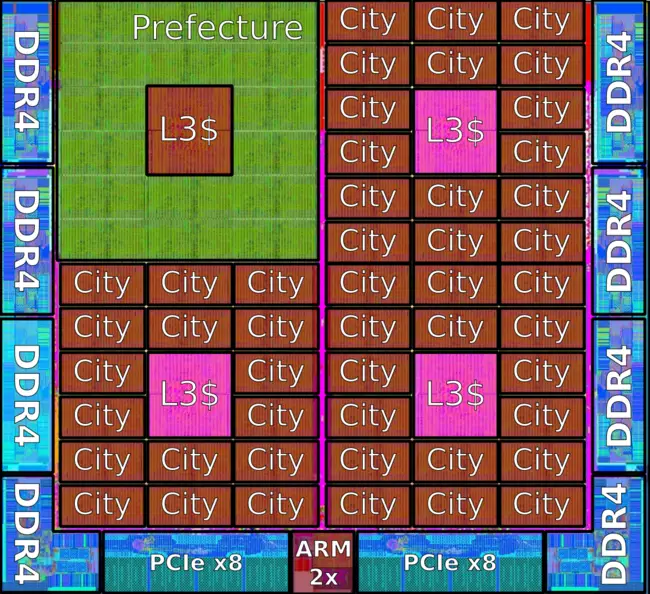

The PEZY-SC microprocessors is made of 4 blocks called "Prefectures". The Prefecture contains 2 MiB of L3$ enclosed by 16 smaller blocks called "Cities". Each City is made of 64 KiB of L2$, a number of special function units, and 4 smaller blocks called "Villages". A village is a block of 4 execution units. For every 2 execution units there is 2 KiB of L1D$.

Cache

PEZY-SC's cache is separate from the ARM926's cache which has an L1$ of 32 KiB (2x) and 64 KiB L2$ (shared).

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Additionally, there is another 16 MiB consisting of 16 KiB per PE of scratch pad memory.

Memory controller

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions

Expansion Options |

|||||

|

|||||

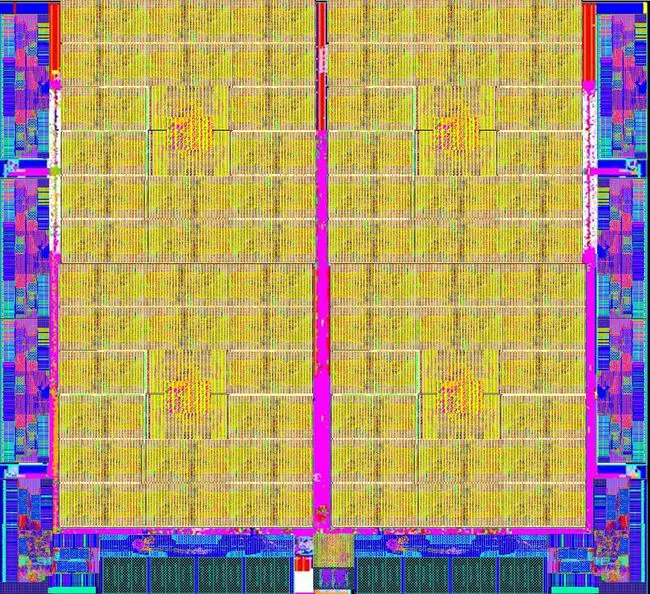

Die Shot

- 28 nm process

- 19.5 mm × 21.1 mm

- 411.6 mm² die size

External Links

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | PEZY-SC - PEZY#pcie + |

| has ecc memory support | true + |

| l1$ size | 3,072 KiB (3,145,728 B, 3 MiB) + |

| l1d$ description | per 2 processor elements + |

| l1d$ size | 1,024 KiB (1,048,576 B, 1 MiB) + |

| l1i$ description | per processor element + |

| l1i$ size | 2,048 KiB (2,097,152 B, 2 MiB) + |

| l2$ description | per city + |

| l2$ size | 4 MiB (4,096 KiB, 4,194,304 B, 0.00391 GiB) + |

| l3$ description | per prefecture + |

| l3$ size | 8 MiB (8,192 KiB, 8,388,608 B, 0.00781 GiB) + |

| max memory bandwidth | 127.156 GiB/s (130,207.744 MiB/s, 136.533 GB/s, 136,532.715 MB/s, 0.124 TiB/s, 0.137 TB/s) + |

| max memory channels | 8 + |

| peak flops (double-precision) | 1,501,866,665,984 FLOPS (1,501,866,665.984 KFLOPS, 1,501,866.666 MFLOPS, 1,501.867 GFLOPS, 1.502 TFLOPS, 0.0015 PFLOPS, 1.501867e-6 EFLOPS, 1.501867e-9 ZFLOPS) + |

| peak flops (single-precision) | 3,003,733,331,968 FLOPS (3,003,733,331.968 KFLOPS, 3,003,733.332 MFLOPS, 3,003.733 GFLOPS, 3.004 TFLOPS, 0.003 PFLOPS, 3.003733e-6 EFLOPS, 3.003733e-9 ZFLOPS) + |

| supported memory type | DDR4-2133 + |