From WikiChip

Difference between revisions of "ampere computing/microarchitectures/quicksilver"

m (Reverted edits by 4.28.13.142 (talk) to last revision by David) |

(typo) |

||

| Line 19: | Line 19: | ||

== Release Dates == | == Release Dates == | ||

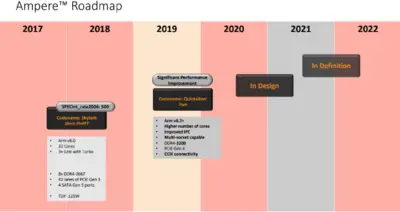

[[File:ampere quicksilver roadmap.png|right|400px]] | [[File:ampere quicksilver roadmap.png|right|400px]] | ||

| − | Quicksilver is planned to be launched | + | Quicksilver is planned to be launched sometime in 2019. |

== Technology == | == Technology == | ||

Revision as of 19:25, 23 August 2019

| Edit Values | |

| Quicksilver µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Ampere Computing |

| Manufacturer | TSMC |

| Introduction | 2019 |

| Process | 7 nm |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | ARMv8.2 |

| Succession | |

Quicksilver is Ampere's successor to Skylark, a planned 7 nm ARM microarchitecture for servers.

Release Dates

Quicksilver is planned to be launched sometime in 2019.

Technology

Quicksilver will be fabricated on TSMC's 7 nm process.

Architecture

Key changes from Skylark

- 7 nm process (from 16 nm)

- Higher IPC

- Higher core count (from 32-core)

- ARMv8.2 support (from ARMv8)

- Multi-socket support

- Faster memory (3200 MT/s from 2666 MT/s)

- PCIe 4.0 support (from 3.0)

- CCIX connectivity support

Facts about "Quicksilver - Microarchitectures - Ampere"

| codename | Quicksilver + |

| designer | Ampere Computing + |

| first launched | 2019 + |

| full page name | ampere computing/microarchitectures/quicksilver + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8.2 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Quicksilver + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + |