From WikiChip

Difference between revisions of "intel/microarchitectures/sapphire rapids"

(→Key changes from {{\\|Ice Lake (server)|Ice Lake}}) |

|||

| Line 28: | Line 28: | ||

* Core | * Core | ||

** {{\\|Sunny Cove}} '''→''' {{\\|Willow Cove}} | ** {{\\|Sunny Cove}} '''→''' {{\\|Willow Cove}} | ||

| + | * Memory Controller | ||

| + | ** DDR5 (from DDR4) | ||

| + | * I/O | ||

| + | ** PCIe Gen 5.0 (from Gen 4.0) | ||

* Platform | * Platform | ||

** {{intel|Whitley|l=platform}} '''→''' {{intel|Eagle Stream|l=platform}} | ** {{intel|Whitley|l=platform}} '''→''' {{intel|Eagle Stream|l=platform}} | ||

{{expand list}} | {{expand list}} | ||

Revision as of 14:08, 21 May 2019

| Edit Values | |

| Sapphire Rapids µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | 2021 |

| Process | 10 nm |

| Instructions | |

| ISA | x86-64 |

| Succession | |

Sapphire Rapids (SPR) is Intel's successor to Ice Lake, a 10 nm microarchitecture for enthusiasts and servers.

History

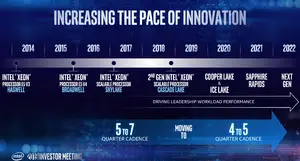

Sapphire Rapids was first announced during the May 2019 Intel Investor Meeting. Sapphire Rapids is planned to succeed Ice Lake in 2021.

Process Technology

Sapphire Rapids is planned to be manufactured on Intel's 3rd generation enhanced 10nm++ process.

Architecture

Key changes from Ice Lake

- 10 nm++ process (from 10 nm+)

- Core

- Memory Controller

- DDR5 (from DDR4)

- I/O

- PCIe Gen 5.0 (from Gen 4.0)

- Platform

This list is incomplete; you can help by expanding it.

Facts about "Sapphire Rapids - Microarchitectures - Intel"

| codename | Sapphire Rapids + |

| designer | Intel + |

| first launched | 2021 + |

| full page name | intel/microarchitectures/sapphire rapids + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Sapphire Rapids + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |