(→Die) |

|||

| Line 1: | Line 1: | ||

{{ibm title|Centaur}} | {{ibm title|Centaur}} | ||

| − | '''Centaur''' | + | '''Centaur''' is a memory buffer chip designed by [[IBM]] for their {{ibm|POWER}} scale-up microprocessors. First introduced with the {{ibm|POWER8|l=arch}} microarchitecture, each Centaur chip includes 16 MiB of [[eDRAM]] and four DDR3/DDR4 [[DRAM]] ports. |

== Overview == | == Overview == | ||

Revision as of 23:20, 27 September 2018

Centaur is a memory buffer chip designed by IBM for their POWER scale-up microprocessors. First introduced with the POWER8 microarchitecture, each Centaur chip includes 16 MiB of eDRAM and four DDR3/DDR4 DRAM ports.

Contents

Overview

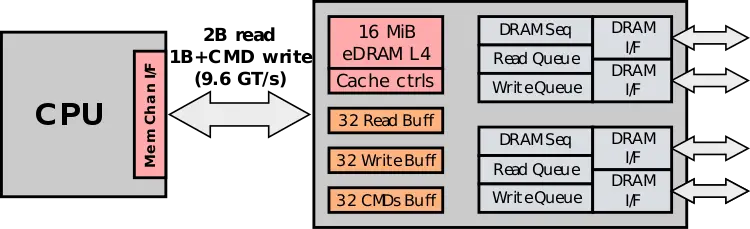

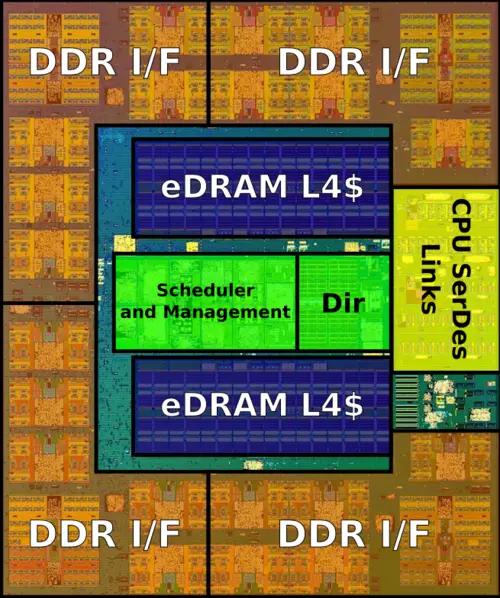

Due to the inherent limitations of scaling DDR to a large number of channels, IBM uses an array of SerDes on the POWER die in order to communicate with an intermediate memory buffer chip, called Centaur, which is used to access a larger set of DDR devices. Centaur is fabricated on 22 nm SOI, has 16 MiB of eDRAM, and includes four 9 or 10B (1 byte spare) DRAM ports supporting both JEDEC DDR3 and DDR4. DRAM ports are accessed in pairs, fetching 128 B cache lines/port-pair. Each port can address up to 16 logically independent DRAM ranks providing support for multiple physical memory ranks.

POWER8 and POWER9 processors that rely on Centaur communicate in a memory-channel-agnostic way. Operations such as cache-line reads/writes are sent to the chip as high-level commands. Scheduling is no longer tightly controlled by the microprocessor as it did in prior designs (e.g., POWER7. It's worth noting that the agnostic attribute of Centaur, new memory technologies (e.g., storage-class memory) can be introduced without any fundamental changes to the microprocessor itself.

Mechanism

Both POWER8 and POWER9 have two memory controllers capable of driving four differential memory interface (DMI) channels, each with a maximum signaling rate of 9.6 GT/s. Each channel provides 2B wide read and 1B wide write for a sustained bandwidth of up to 28.8 GB/s. Each of the DMI channels connects to a dedicated Centaur chip which, in turn, provides four DDR4 memory channels running at up to 3200 MT/s as well as 16 MiB of L4 cache. In other words, with this configuration, a single processor can use eight buffered memory channels to access up to 32 channels of DDR memory and another 128 MiB of L4 buffer cache. Note that each buffer chip DDR4 port supports a single DDR4 DIMM.

Centaur operates on high-level commands sent from the microprocessor. Requests are handled as quickly as possible. The chip is capable of reordering DRAM requests and since there is a large level 4 cache on-die, requests hitting the cache are sent right away, meaning some requests may be reordered.

Centaur incorporates 16 MiB of L4 buffer cache for a total of 128 MiB with all eight channels and chips. The L4 cache is used exclusively as a buffer for memory and is only accessed on memory-system accesses meaning it does not part take in any of the microprocessor coherence protocols (i.e., not snooped). The cache is 16-way set-associative with data stored in eDRAM and the directory in SRAM. An L4 buffer cache hit reduces L3 miss latency considerably. It also allows the system to quickly retire writes because every write operation is written to the L4 first in order to free it from the memory controller queue. Writes then written to memory at the buffer memory's earliest convenience.

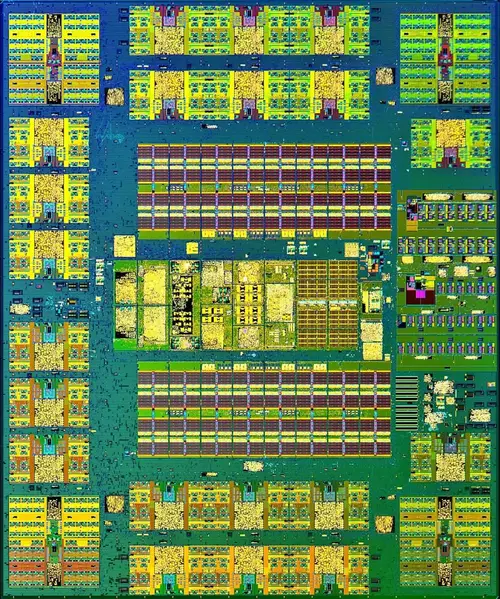

Die