| Line 7: | Line 7: | ||

== Registers == | == Registers == | ||

A64 has 31 [[general-purpose registers]], all of which are 64-bit wide. Depending on the instruction, the 32nd register is used to obtain a zero or the stack pointer. The almost doubling of the GPR count was done in order to improve both the performance and power of the implementations (designed to reduce cache accesses). Banking was eliminated altogether. Additionally, the stack pointer is no longer regarded as a GPR and the [[program counter]] is no longer treated as a normal directly accessible register. | A64 has 31 [[general-purpose registers]], all of which are 64-bit wide. Depending on the instruction, the 32nd register is used to obtain a zero or the stack pointer. The almost doubling of the GPR count was done in order to improve both the performance and power of the implementations (designed to reduce cache accesses). Banking was eliminated altogether. Additionally, the stack pointer is no longer regarded as a GPR and the [[program counter]] is no longer treated as a normal directly accessible register. | ||

| + | |||

| + | === Packing === | ||

| + | Compared to {{\\|A32}}, smaller registers no longer packed into the larger ones but are instead mapped one-to-one to the low-order bits of the bigger register. | ||

| + | |||

| + | :[[File:arm a64 registers.svg|400px]] | ||

== Instructions == | == Instructions == | ||

| Line 12: | Line 17: | ||

== Advanced SIMD == | == Advanced SIMD == | ||

| − | A64 Advanced SIMD ({{\\|NEON}}) shares the same register file as the {{\\|A32}} floating-point [[register file]] but is extended to 128-bit. A64 has 32 128-bit wide vector registers (this is double the amount from {{\\|A32}}) | + | A64 Advanced SIMD ({{\\|NEON}}) shares the same register file as the {{\\|A32}} floating-point [[register file]] but is extended to 128-bit. A64 has 32 128-bit wide vector registers (this is double the amount from {{\\|A32}}). A64 advanced SIMD added support for [[double-precision floating point]] as well as [[IEE 754]] compliance. Additional instructions were also added to support the 2008 version fo the standard (e.g., conversion, min/max). |

== Bibliography == | == Bibliography == | ||

* Richard Grisenthwaite. (October 26, 2011). ''"Technology Preview: The ARM Architecture - a View of the Future "''. | * Richard Grisenthwaite. (October 26, 2011). ''"Technology Preview: The ARM Architecture - a View of the Future "''. | ||

* ARM Architecture Group. "Armv8 instruction set overview." vol. PRD03-GENC-010197 (2011). | * ARM Architecture Group. "Armv8 instruction set overview." vol. PRD03-GENC-010197 (2011). | ||

Revision as of 16:05, 20 September 2018

| ARM ISA | |

| General | |

| Variants | |

| Extensions | |

| Topics | |

| Versions(all) | |

A64 is a 32-bit fixed-length instruction set that machines in AArch64 state execute. This instruction set was introduced with the ARMv8 ISA.

Overview

The A64 instruction set was introduced with the ARMv8 ISA in order to introduce 64-bit capabilities, primarily targeting the LP64 and LPP64 64-bit data models. It is fixed-length with instructions being 32 bits in size and follow almost identical semantics as in AArch32. This was done in order to maximize the hardware reuse. With the exception of branches and comparisons, predication was also eliminted. Compared to the 32-bit instruction set which offered 14 general-purpose registers, the A64 IS has 31 GPRs. Most instructions are capable of having a 32-bit or 64-bit operand and the address is assumed to be 64-bit in size.

Registers

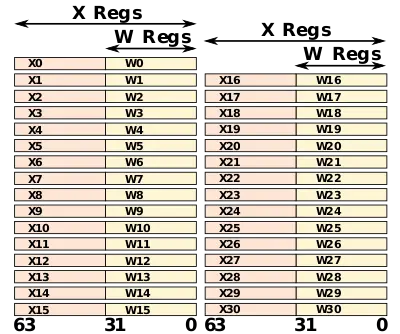

A64 has 31 general-purpose registers, all of which are 64-bit wide. Depending on the instruction, the 32nd register is used to obtain a zero or the stack pointer. The almost doubling of the GPR count was done in order to improve both the performance and power of the implementations (designed to reduce cache accesses). Banking was eliminated altogether. Additionally, the stack pointer is no longer regarded as a GPR and the program counter is no longer treated as a normal directly accessible register.

Packing

Compared to A32, smaller registers no longer packed into the larger ones but are instead mapped one-to-one to the low-order bits of the bigger register.

Instructions

Most instructions are capable of supporting both 32-bit or 64-bit operands. A64 primarily targeted the LP64 and LPP64 data models, meaning long, long long integers, and pointers are 64-bit wide while integers are 32 bit. A64 has a limited set of instructions supporting predication and arbitrary length load/store are no longer supported.

Advanced SIMD

A64 Advanced SIMD (NEON) shares the same register file as the A32 floating-point register file but is extended to 128-bit. A64 has 32 128-bit wide vector registers (this is double the amount from A32). A64 advanced SIMD added support for double-precision floating point as well as IEE 754 compliance. Additional instructions were also added to support the 2008 version fo the standard (e.g., conversion, min/max).

Bibliography

- Richard Grisenthwaite. (October 26, 2011). "Technology Preview: The ARM Architecture - a View of the Future ".

- ARM Architecture Group. "Armv8 instruction set overview." vol. PRD03-GENC-010197 (2011).