From WikiChip

Difference between revisions of "intel/atom/z510"

(+q-spec) |

|||

| Line 19: | Line 19: | ||

| last order = | | last order = | ||

| last shipment = | | last shipment = | ||

| − | | release price = | + | | release price = $45 |

| family = Atom | | family = Atom | ||

| Line 69: | Line 69: | ||

}} | }} | ||

'''Z510''' is an ultra-low power {{arch|32}} [[x86]] microprocessor introduced by [[Intel]] in early 2008 specifically for Mobile Internet Devices (MID). The Z510, which is based on the {{intel|Bonnell|l=arch}} microarchitecture ({{intel|Silverthorne|l=core}} core), is manufactured on a [[45 nm process]]. This processor operates at 1.1 Ghz with a TDP of just 2 W and an average power of 220 mW. The MPU features a legacy 400 MT/s [[front-side bus]] capable of communicating with the {{intel|Poulsbo|l=chipset}} chipset in both low-power [[CMOS]] mode as well as normal [[GTL]] mode (which also works with other chipsets). | '''Z510''' is an ultra-low power {{arch|32}} [[x86]] microprocessor introduced by [[Intel]] in early 2008 specifically for Mobile Internet Devices (MID). The Z510, which is based on the {{intel|Bonnell|l=arch}} microarchitecture ({{intel|Silverthorne|l=core}} core), is manufactured on a [[45 nm process]]. This processor operates at 1.1 Ghz with a TDP of just 2 W and an average power of 220 mW. The MPU features a legacy 400 MT/s [[front-side bus]] capable of communicating with the {{intel|Poulsbo|l=chipset}} chipset in both low-power [[CMOS]] mode as well as normal [[GTL]] mode (which also works with other chipsets). | ||

| + | |||

| + | Model price includes the {{intel|Poulsbo|chipset|l=chipset}}. | ||

== Cache == | == Cache == | ||

Revision as of 03:59, 2 April 2017

Template:mpu Z510 is an ultra-low power 32-bit x86 microprocessor introduced by Intel in early 2008 specifically for Mobile Internet Devices (MID). The Z510, which is based on the Bonnell microarchitecture (Silverthorne core), is manufactured on a 45 nm process. This processor operates at 1.1 Ghz with a TDP of just 2 W and an average power of 220 mW. The MPU features a legacy 400 MT/s front-side bus capable of communicating with the Poulsbo chipset in both low-power CMOS mode as well as normal GTL mode (which also works with other chipsets).

Model price includes the chipset.

Cache

- Main article: Bonnell § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller

This processor has no integrated memory controller.

Graphics

This processor has no integrated graphics.

Features

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||

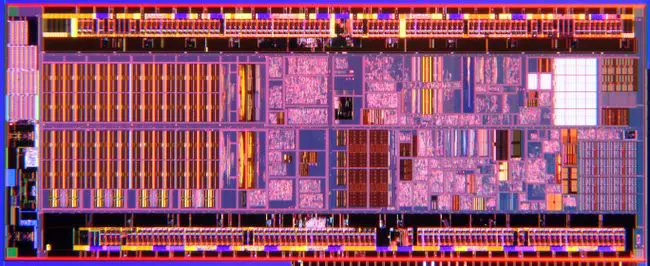

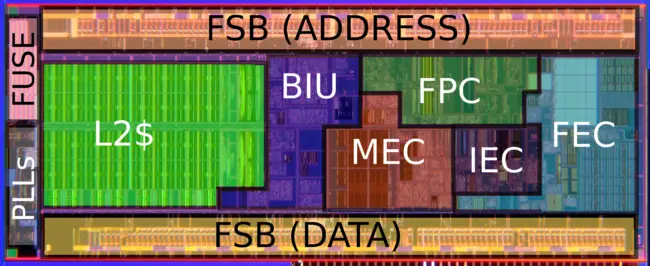

Die Shot

- See also: Bonnell § Silverthorne Die

- 45 nm process

- 9 metal layers

- 47,212,207 transistors

- 3.1 mm x 7.8 mm

- 24.18 mm² die size

Documents

Datasheet

Facts about "Atom Z510 - Intel"

| has feature | Enhanced SpeedStep Technology + |

| has intel enhanced speedstep technology | true + |

| l1$ size | 56 KiB (57,344 B, 0.0547 MiB) + |

| l1d$ description | 6-way set associative + |

| l1d$ size | 24 KiB (24,576 B, 0.0234 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 32 KiB (32,768 B, 0.0313 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |