(→Operation) |

(→Operation: added some illustrations) |

||

| Line 20: | Line 20: | ||

=== Operation === | === Operation === | ||

Static RAMs use basic memory cells with built-in feedback mechanisms that retain the stored value for as long as the device is powered. A basic example of a feedback mechanism is a pair of [[inverters]] that are cross-coupled such that the output of one [[inverter]] becomes the input of the other inverter. As long as there is power, the stored value will be continuously reinforced by the positive feedback loop which also helps correct for leakage and noise. | Static RAMs use basic memory cells with built-in feedback mechanisms that retain the stored value for as long as the device is powered. A basic example of a feedback mechanism is a pair of [[inverters]] that are cross-coupled such that the output of one [[inverter]] becomes the input of the other inverter. As long as there is power, the stored value will be continuously reinforced by the positive feedback loop which also helps correct for leakage and noise. | ||

| + | |||

| + | :[[File:sram_basic.svg|300px]] | ||

Writing a new [[bit]] value involves driving the desired value and its complement onto the input and output of the cross-coupled inverters. By driving a stronger new value and overpowering the older values, a new bit value may be stored in the cell. | Writing a new [[bit]] value involves driving the desired value and its complement onto the input and output of the cross-coupled inverters. By driving a stronger new value and overpowering the older values, a new bit value may be stored in the cell. | ||

| + | |||

| + | :[[File:sram basic override.svg|400px]] | ||

Reading the stored value involves reading the output of the cell. Note that in practice, due to the size of the transistors involved which makes them very weak, driving the output directly from the bitcell is very challenging. Instead, a [[sense amplifier]] is used to generate a strong output from the attenuated bit value. This is explained in more detail later in this article. | Reading the stored value involves reading the output of the cell. Note that in practice, due to the size of the transistors involved which makes them very weak, driving the output directly from the bitcell is very challenging. Instead, a [[sense amplifier]] is used to generate a strong output from the attenuated bit value. This is explained in more detail later in this article. | ||

Revision as of 22:44, 27 October 2019

Static random-access memory (Static RAM or SRAM) is a simple semiconductor memory device that implements a random-access memory-based storage that holds data in a static form. That is, static RAM retains its data for as long as the memory device has power. SRAM is the most common type of memory cell found in most VLSI designs.

Contents

Overview

Static Random Access Memory (SRAM) is a type of semiconductor memory. It is static and volatile, implying data retention persists for as long as the device is powered without any form of a refresh, however, once the power is cut, data will be lost. It is random access, meaning the next memory location that can be read or written to does not depend on the last access location. The static property of SRAM comes from its use of some sort of a feedback mechanism to maintain the stored bit state. This is in contrast to other forms of memory, such as Dynamic RAM, where the stored state of the bit is kept in the form of a charge that leaks over time thereby requiring the data to be refreshed (i.e, read and re-written back).

Large blocks of SRAM memory comprise of arrays of individual SRAM blocks called cells. An SRAM cell is capable of storing a single bit of data for as long as there is power. Likewise, an array of eight SRAM cells can store 1 byte of data. Arrays of SRAM form the foundation for every

Applications

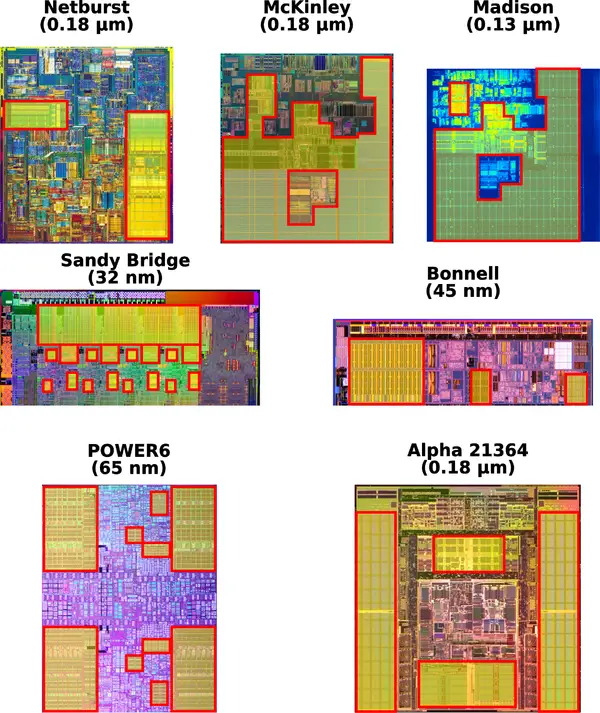

Due to its relative simplicity, SRAM is the most common memory cell found in modern microprocessors. It is used for various large buffers and caches. Current SoCs allocate a large portion of the die to SRAM. For example, in Intel's first-generation Atom processors, codename Bonnell, 30,644,682 out of the 47,212,207 transistors (65%) were dedicated to the level 2 cache. In Intel's Itanium 2, codename Montecito, 90% of the 1.72-billion transistors were occupied by SRAM.

Below are large SRAM blocks highlighted on real-world high-performance microprocessors, showing how much silicon area, SRAM typically occupies. There are many smaller blocks that were not marked.

- Note: Die images NOT to scale.

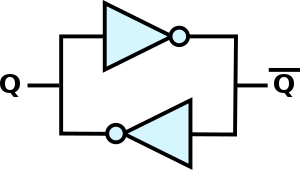

Operation

Static RAMs use basic memory cells with built-in feedback mechanisms that retain the stored value for as long as the device is powered. A basic example of a feedback mechanism is a pair of inverters that are cross-coupled such that the output of one inverter becomes the input of the other inverter. As long as there is power, the stored value will be continuously reinforced by the positive feedback loop which also helps correct for leakage and noise.

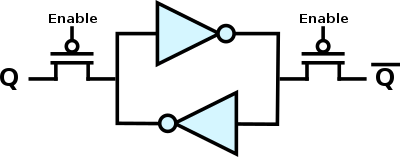

Writing a new bit value involves driving the desired value and its complement onto the input and output of the cross-coupled inverters. By driving a stronger new value and overpowering the older values, a new bit value may be stored in the cell.

Reading the stored value involves reading the output of the cell. Note that in practice, due to the size of the transistors involved which makes them very weak, driving the output directly from the bitcell is very challenging. Instead, a sense amplifier is used to generate a strong output from the attenuated bit value. This is explained in more detail later in this article.

Cells

| This section is empty; you can help add the missing info by editing this page. |

4T Cell

| This section is empty; you can help add the missing info by editing this page. |

6T Cell

| This section is empty; you can help add the missing info by editing this page. |

8T Cell

| This section is empty; you can help add the missing info by editing this page. |

Leading-edge SRAM

| This section is empty; you can help add the missing info by editing this page. |