(typo fix) |

(→Architecture: Papermaster quotes) |

||

| Line 49: | Line 49: | ||

== Architecture == | == Architecture == | ||

| − | Nothing is currently known about the architectural improvements that is being done to Zen 2. | + | Nothing concrete is currently known about the architectural improvements that is being done to Zen 2. |

| + | Papermaster's presentation at Next Horizon quotes "Improved Branch Predictor", "Better Instruction Pre-Fetching", "Re-Optimized Instruction Cache", "Larger Op Cache", "Doubled Floating Point Width to 256-bit", "Doubled Load / Store Bandwidth", "Increased Dispatch / Retire Bandwidth", "Maintained High Throughput for All Modes" without further specifics. | ||

=== Key changes from {{\\|Zen}} === | === Key changes from {{\\|Zen}} === | ||

Revision as of 11:56, 12 November 2018

| Edit Values | |

| Zen 2 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AMD |

| Manufacturer | TSMC |

| Introduction | 2019 |

| Process | 7 nm |

| Succession | |

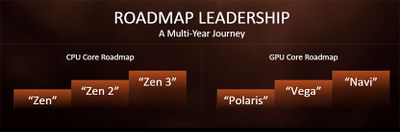

Zen 2 is a planned microarchitecture being developed by AMD as a successor to Zen+. Zen 2 is expected to be succeeded by Zen 3.

Contents

History

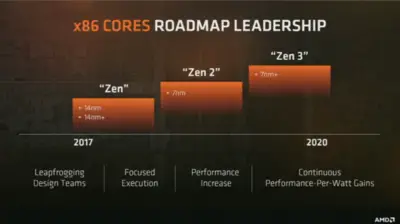

Zen 2 is set to succeed Zen in the future, sometimes around 2019. In February of 2017 Lisa Su, AMD's CEO announced their future roadmap to include Zen 2 and later Zen 3. On Investor's Day May 2017 Jim Anderson, AMD Senior Vice President, confirmed that Zen 2 is set to utilize 7 nm process.

Codenames

| Core | C/T | Target |

|---|---|---|

| Rome | Up to 64/128 | High-end server multiprocessors |

| Castle Peak | ?/? | workstation & enthusiasts market processors |

| Matisse | ?/? | Mainstream to high-end desktops & enthusiasts market processors |

| Picasso | ?/? | Mainstream desktop & mobile processors with GPU |

Process technology

Zen 2 is fabricated on TSMC's 7 nm process.

Compiler support

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| GCC | -march=znver2 |

-mtune=znver2

|

- Note: Initial support in GCC 9.

Architecture

Nothing concrete is currently known about the architectural improvements that is being done to Zen 2. Papermaster's presentation at Next Horizon quotes "Improved Branch Predictor", "Better Instruction Pre-Fetching", "Re-Optimized Instruction Cache", "Larger Op Cache", "Doubled Floating Point Width to 256-bit", "Doubled Load / Store Bandwidth", "Increased Dispatch / Retire Bandwidth", "Maintained High Throughput for All Modes" without further specifics.

Key changes from Zen

- 7 nm process (from 14 nm)

- PCIe 4.0 (from 3.0)

This list is incomplete; you can help by expanding it.

New instructions

Zen 2 introduced a number of new x86 instructions:

-

CLWB- Force cache line write-back without flush -

RDPID- Read Processor ID -

WBNOINVD- Force cache line write-back without invalidation

Bibliography

- AMD 'Tech Day', February 22, 2017

- AMD 2017 Financial Analyst Day, May 16, 2017

- AMD GCC 9 znver2 enablement patch

- AMD 'Next Horizon', November 6, 2018

See Also

- Intel Ice Lake

| codename | Zen 2 + |

| designer | AMD + |

| first launched | 2019 + |

| full page name | amd/microarchitectures/zen 2 + |

| instance of | microarchitecture + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Zen 2 + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + |