| Line 29: | Line 29: | ||

The chip consists of five subsystems: [[NPU]], [[MCU]], Chip Link, Memory, and Peripherals. The MCU Subsystem is a low-power embedded [[ARM]] microcontroller. The NPU Subsystem consists of 64 [[NPUs]], the hub, and an NPU Schedule Engine. The scheduling engine is in charge of controlling the data flow to the individual NPUs. Bitmain has not many intimate details of the NPU cores but each core is known to have 512 KiB of program-visible [[SRAM]] and supports 64 single-precision operations. With a total of 64 NPUs, the chip has a total of 32 [[MiB]] of [[cache]] and a peak performance of 2 [[TFLOPS]] (single-precision). | The chip consists of five subsystems: [[NPU]], [[MCU]], Chip Link, Memory, and Peripherals. The MCU Subsystem is a low-power embedded [[ARM]] microcontroller. The NPU Subsystem consists of 64 [[NPUs]], the hub, and an NPU Schedule Engine. The scheduling engine is in charge of controlling the data flow to the individual NPUs. Bitmain has not many intimate details of the NPU cores but each core is known to have 512 KiB of program-visible [[SRAM]] and supports 64 single-precision operations. With a total of 64 NPUs, the chip has a total of 32 [[MiB]] of [[cache]] and a peak performance of 2 [[TFLOPS]] (single-precision). | ||

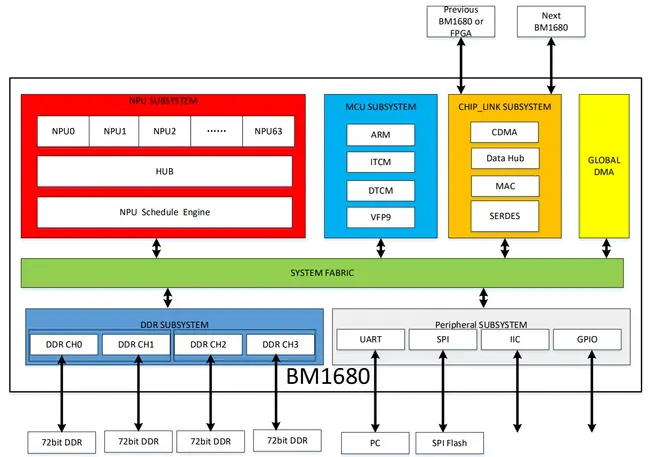

| − | :[[File:BM1680 block diagram.png| | + | :[[File:BM1680 block diagram.png|650px]] |

Revision as of 16:29, 18 November 2017

Template:mpu Sophon BM1680 is a neural processor designed by Bitmain and introduced in 2017. The BM1680 is capable of performing both network inference and network training.

Manufactured on TSMC's 28HPC+ process, the BM1680 is capable of 80 billion algorithmic operations per second. Bitmain claims the chip is designed not only for inference, but also for training of neural networks, suitable for working with the common ANNs such as CNN, RNN, and DNN.

Overview

The chip consists of five subsystems: NPU, MCU, Chip Link, Memory, and Peripherals. The MCU Subsystem is a low-power embedded ARM microcontroller. The NPU Subsystem consists of 64 NPUs, the hub, and an NPU Schedule Engine. The scheduling engine is in charge of controlling the data flow to the individual NPUs. Bitmain has not many intimate details of the NPU cores but each core is known to have 512 KiB of program-visible SRAM and supports 64 single-precision operations. With a total of 64 NPUs, the chip has a total of 32 MiB of cache and a peak performance of 2 TFLOPS (single-precision).