From WikiChip

Difference between revisions of "amd/ryzen 7/2700u"

| Line 35: | Line 35: | ||

This model supports a configurable TDP-down of 12 W and TDP-up of 25 W. | This model supports a configurable TDP-down of 12 W and TDP-up of 25 W. | ||

| + | |||

| + | == Cache == | ||

| + | {{main|amd/microarchitectures/zen#Memory_Hierarchy|l1=Zen § Cache}} | ||

| + | {{cache size | ||

| + | |l1 cache=384 KiB | ||

| + | |l1i cache=256 KiB | ||

| + | |l1i break=4x64 KiB | ||

| + | |l1i desc=4-way set associative | ||

| + | |l1d cache=128 KiB | ||

| + | |l1d break=4x32 KiB | ||

| + | |l1d desc=8-way set associative | ||

| + | |l1d policy=write-back | ||

| + | |l2 cache=2 MiB | ||

| + | |l2 break=4x512 KiB | ||

| + | |l2 desc=8-way set associative | ||

| + | |l2 policy=write-back | ||

| + | |l3 cache=4 MiB | ||

| + | |l3 break=1x4 MiB | ||

| + | }} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR4-2400 | ||

| + | |max mem=? GiB | ||

| + | |controllers=2 | ||

| + | |channels=2 | ||

| + | |max bandwidth=35.76 GiB/s | ||

| + | |bandwidth schan=17.88 GiB/s | ||

| + | |bandwidth dchan=35.76 GiB/s | ||

| + | }} | ||

| + | |||

| + | == Expansions == | ||

| + | {{expansions main | ||

| + | | | ||

| + | {{expansions entry | ||

| + | |type=PCIe | ||

| + | |pcie revision=3.0 | ||

| + | |pcie lanes=? | ||

| + | |pcie config=x? | ||

| + | }} | ||

| + | }} | ||

| + | |||

| + | == Features == | ||

| + | {{x86 features | ||

| + | |real=Yes | ||

| + | |protected=Yes | ||

| + | |smm=Yes | ||

| + | |fpu=Yes | ||

| + | |x8616=Yes | ||

| + | |x8632=Yes | ||

| + | |x8664=Yes | ||

| + | |nx=Yes | ||

| + | |mmx=Yes | ||

| + | |emmx=Yes | ||

| + | |sse=Yes | ||

| + | |sse2=Yes | ||

| + | |sse3=Yes | ||

| + | |ssse3=Yes | ||

| + | |sse41=Yes | ||

| + | |sse42=Yes | ||

| + | |sse4a=Yes | ||

| + | |avx=Yes | ||

| + | |avx2=Yes | ||

| + | |||

| + | |abm=Yes | ||

| + | |tbm=No | ||

| + | |bmi1=Yes | ||

| + | |bmi2=Yes | ||

| + | |fma3=Yes | ||

| + | |fma4=No | ||

| + | |aes=Yes | ||

| + | |rdrand=Yes | ||

| + | |sha=Yes | ||

| + | |xop=No | ||

| + | |adx=Yes | ||

| + | |clmul=Yes | ||

| + | |f16c=Yes | ||

| + | |tbt1=No | ||

| + | |tbt2=No | ||

| + | |tbmt3=No | ||

| + | |bpt=No | ||

| + | |eist=No | ||

| + | |sst=No | ||

| + | |flex=No | ||

| + | |fastmem=No | ||

| + | |isrt=No | ||

| + | |sba=No | ||

| + | |mwt=No | ||

| + | |sipp=No | ||

| + | |att=No | ||

| + | |ipt=No | ||

| + | |tsx=No | ||

| + | |txt=No | ||

| + | |ht=No | ||

| + | |vpro=No | ||

| + | |vtx=No | ||

| + | |vtd=No | ||

| + | |ept=No | ||

| + | |mpx=No | ||

| + | |sgx=No | ||

| + | |securekey=No | ||

| + | |osguard=No | ||

| + | |3dnow=No | ||

| + | |e3dnow=No | ||

| + | |smartmp=No | ||

| + | |powernow=No | ||

| + | |amdvi=Yes | ||

| + | |amdv=Yes | ||

| + | |rvi=No | ||

| + | |smt=Yes | ||

| + | |sensemi=Yes | ||

| + | |xfr=Yes | ||

| + | }} | ||

| + | |||

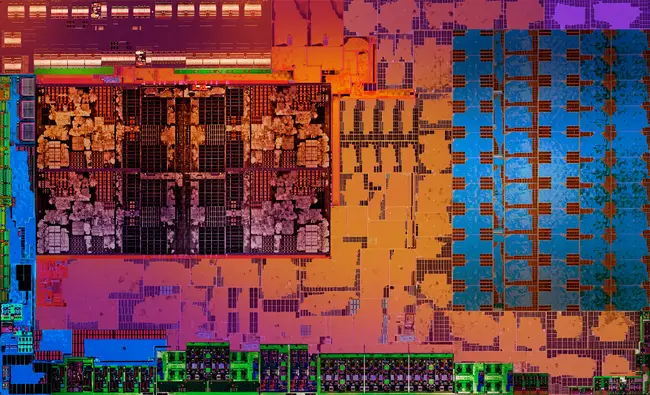

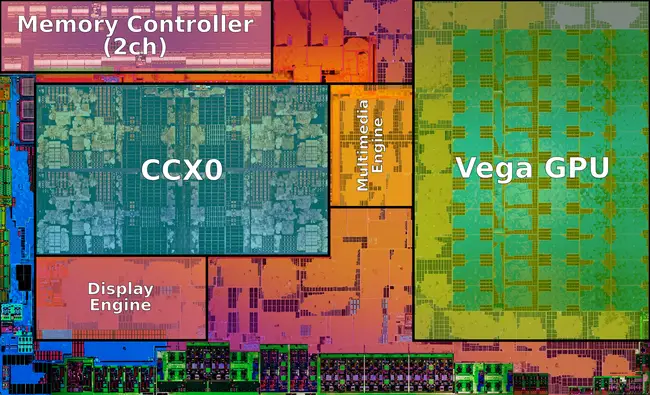

| + | == Die Shot == | ||

| + | {{further|amd/microarchitectures/zen#Die|l1=Zen § Die Shot}} | ||

| + | * [[14 nm process]] | ||

| + | * 4,950,000,000 transistors | ||

| + | * 209.78 mm² die size | ||

| + | |||

| + | |||

| + | : [[File:raven ridge die.png|650px]] | ||

| + | |||

| + | |||

| + | : [[File:raven ridge die (annotated).png|650px]] | ||

Revision as of 23:39, 26 October 2017

Template:mpu Ryzen 7 2700U is a 64-bit quad-core high-end performance x86 mobile microprocessor introduced by AMD in late 2017. This processor is based on AMD's Zen microarchitecture and is fabricated on a 14 nm process. The 2700U operates at a base frequency of 2.2 GHz with a TDP of 15 W and a Boost frequency of 3.8 GHz. This MPU supports up to ? GiB of dual-channel DDR4-2400 memory and incorporates Radeon Vega 10 Graphics operating at up to 1.1 GHz.

This model supports a configurable TDP-down of 12 W and TDP-up of 25 W.

Cache

- Main article: Zen § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||

|

||||||||||||

Expansions

Expansion Options |

|||||

|

|||||

Features

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Die Shot

- Further information: Zen § Die Shot

- 14 nm process

- 4,950,000,000 transistors

- 209.78 mm² die size

Facts about "Ryzen 7 2700U - AMD"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Ryzen 7 2700U - AMD#pcie + |

| base frequency | 2,200 MHz (2.2 GHz, 2,200,000 kHz) + |

| chipset | Promontory + |

| clock multiplier | 22 + |

| core count | 4 + |

| core family | 23 + |

| core model | 1 + |

| core name | Raven Ridge + |

| designer | AMD + |

| die area | 209.78 mm² (0.325 in², 2.098 cm², 209,780,000 µm²) + |

| family | Ryzen 7 + |

| first announced | October 26, 2017 + |

| first launched | October 26, 2017 + |

| full page name | amd/ryzen 7/2700u + |

| has advanced vector extensions | true + |

| has advanced vector extensions 2 | true + |

| has amd amd-v technology | true + |

| has amd amd-vi technology | true + |

| has amd extended frequency range | true + |

| has amd sensemi technology | true + |

| has ecc memory support | true + |

| has feature | Advanced Vector Extensions +, Advanced Vector Extensions 2 +, Advanced Encryption Standard Instruction Set Extension +, SenseMI Technology + and Extended Frequency Range + |

| has locked clock multiplier | true + |

| has simultaneous multithreading | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| instance of | microprocessor + |

| integrated gpu | Radeon Vega 10 + |

| integrated gpu designer | AMD + |

| integrated gpu execution units | 10 + |

| integrated gpu max frequency | 1,300 MHz (1.3 GHz, 1,300,000 KHz) + |

| isa | x86-64 + |

| isa family | x86 + |

| l1$ size | 384 KiB (393,216 B, 0.375 MiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 256 KiB (262,144 B, 0.25 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 2 MiB (2,048 KiB, 2,097,152 B, 0.00195 GiB) + |

| l3$ size | 4 MiB (4,096 KiB, 4,194,304 B, 0.00391 GiB) + |

| ldate | October 26, 2017 + |

| manufacturer | GlobalFoundries + |

| market segment | Mobile + |

| max cpu count | 1 + |

| max memory | 32,768 MiB (33,554,432 KiB, 34,359,738,368 B, 32 GiB, 0.0313 TiB) + |

| max memory bandwidth | 35.76 GiB/s (36,618.24 MiB/s, 38.397 GB/s, 38,397.008 MB/s, 0.0349 TiB/s, 0.0384 TB/s) + |

| max memory channels | 2 + |

| microarchitecture | Zen + |

| model number | 2700U + |

| name | Ryzen 7 2700U + |

| package | BGA-1140 + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| series | 2000U + |

| smp max ways | 1 + |

| supported memory type | DDR4-2400 + |

| tdp | 15 W (15,000 mW, 0.0201 hp, 0.015 kW) + |

| tdp down | 12 W (12,000 mW, 0.0161 hp, 0.012 kW) + |

| tdp up | 25 W (25,000 mW, 0.0335 hp, 0.025 kW) + |

| technology | CMOS + |

| thread count | 8 + |

| transistor count | 4,950,000,000 + |

| turbo frequency (1 core) | 3,800 MHz (3.8 GHz, 3,800,000 kHz) + |

| word size | 64 bit (8 octets, 16 nibbles) + |