From WikiChip

Difference between revisions of "arm holdings/microarchitectures/cortex-a72"

(update) |

m (typo) |

||

| (2 intermediate revisions by 2 users not shown) | |||

| Line 12: | Line 12: | ||

|successor link=arm_holdings/microarchitectures/cortex-a73 | |successor link=arm_holdings/microarchitectures/cortex-a73 | ||

}} | }} | ||

| − | '''Cortex-A72''' (codename ''' | + | '''Cortex-A72''' (codename '''Maia''') is the successor to the {{armh|Cortex-A57|l=arch}}, a low-power high-performance [[ARM]] [[microarchitecture]] designed by [[ARM Holdings]] for the mobile market. This microarchitecture is designed as a synthesizable [[IP core]] and is sold to other semiconductor companies to be implemented in their own chips. The Cortex-A72, which implemented the {{arm|ARMv8}} ISA, is a performant core which is often combined with a number of lower power cores (e.g. {{\\|Cortex-A53}}) in a {{armh|big.LITTLE}} configuration to achieve better energy/performance. |

== Compiler support == | == Compiler support == | ||

| Line 26: | Line 26: | ||

|} | |} | ||

| − | If the Cortex-A72 is coupled with the {{\\|Cortex-A53}} or the {{\\|Cortex-A35}} in a [[big.LITTLE]] system, GCC also supports the following | + | If the Cortex-A72 is coupled with the {{\\|Cortex-A53}} or the {{\\|Cortex-A35}} in a [[big.LITTLE]] system, GCC also supports the following option: |

{| class="wikitable" | {| class="wikitable" | ||

| Line 39: | Line 39: | ||

{{empty section}} | {{empty section}} | ||

=== Block Diagram === | === Block Diagram === | ||

| − | + | {{empty section}} | |

=== Memory Hierarchy === | === Memory Hierarchy === | ||

| − | + | {{empty section}} | |

| + | |||

== Die == | == Die == | ||

=== MediaTek [[Helio X20]] === | === MediaTek [[Helio X20]] === | ||

Latest revision as of 14:57, 4 July 2022

| Edit Values | |

| Cortex-A72 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | ARM Holdings |

| Manufacturer | TSMC |

| Introduction | April 23, 2015 |

| Instructions | |

| ISA | ARMv8 |

| Succession | |

Cortex-A72 (codename Maia) is the successor to the Cortex-A57, a low-power high-performance ARM microarchitecture designed by ARM Holdings for the mobile market. This microarchitecture is designed as a synthesizable IP core and is sold to other semiconductor companies to be implemented in their own chips. The Cortex-A72, which implemented the ARMv8 ISA, is a performant core which is often combined with a number of lower power cores (e.g. Cortex-A53) in a big.LITTLE configuration to achieve better energy/performance.

Contents

Compiler support[edit]

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| Arm Compiler | -mcpu=cortex-a72 |

-mtune=cortex-a72

|

| GCC | -mcpu=cortex-a72 |

-mtune=cortex-a72

|

| LLVM | -mcpu=cortex-a72 |

-mtune=cortex-a72

|

If the Cortex-A72 is coupled with the Cortex-A53 or the Cortex-A35 in a big.LITTLE system, GCC also supports the following option:

| Compiler | Tune |

|---|---|

| GCC | -mtune=cortex-a72.cortex-a53-mtune=cortex-a72.cortex-a35

|

Architecture[edit]

Key changes from Cortex-A57[edit]

| This section is empty; you can help add the missing info by editing this page. |

Block Diagram[edit]

| This section is empty; you can help add the missing info by editing this page. |

Memory Hierarchy[edit]

| This section is empty; you can help add the missing info by editing this page. |

Die[edit]

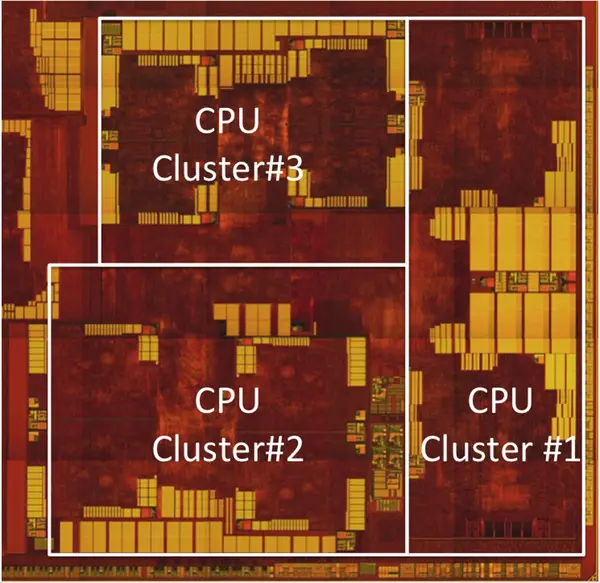

MediaTek Helio X20[edit]

- TSMC 20 nm process

- 100 mm² die size

- Quad-core ULP Cortex-A53

- ~21.81 mm² per cluster

- ~4.23 mm² per core

- ~21.81 mm² per cluster

- Quad-core efficient Cortex-A53

- ~29.73 mm² per cluster

- ~5.41 mm² per core

- ~29.73 mm² per cluster

- Dual-core High-performance Cortex-A72 + 1 MiB L2

- ~27.36 mm² per cluster

- ~ 9.60 mm² per core

- ~ 7.50 mm² for 1 MiB L2

- ~27.36 mm² per cluster

Bibliography[edit]

- Mair, Hugh T., et al. "4.3 A 20nm 2.5 GHz ultra-low-power tri-cluster CPU subsystem with adaptive power allocation for optimal mobile SoC performance." Solid-State Circuits Conference (ISSCC), 2016 IEEE International. IEEE, 2016.

Facts about "Cortex-A72 - Microarchitectures - ARM"

| codename | Cortex-A72 + |

| designer | ARM Holdings + |

| first launched | April 23, 2015 + |

| full page name | arm holdings/microarchitectures/cortex-a72 + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Cortex-A72 + |