From WikiChip

Difference between revisions of "intel/microarchitectures/sapphire rapids"

| (13 intermediate revisions by 8 users not shown) | |||

| Line 5: | Line 5: | ||

|designer=Intel | |designer=Intel | ||

|manufacturer=Intel | |manufacturer=Intel | ||

| − | |introduction= | + | |introduction=2023 |

| − | |process= | + | |process=Intel 7 |

|isa=x86-64 | |isa=x86-64 | ||

|predecessor=Ice Lake (server) | |predecessor=Ice Lake (server) | ||

|predecessor link=intel/microarchitectures/ice lake (server) | |predecessor link=intel/microarchitectures/ice lake (server) | ||

| − | |successor= | + | |successor=Emerald Rapids |

| − | |successor link=intel/microarchitectures/ | + | |successor link=intel/microarchitectures/emerald rapids |

|succession=Yes | |succession=Yes | ||

}} | }} | ||

| − | '''Sapphire Rapids''' ('''SPR''') is [[Intel]]'s successor to {{\\|Ice Lake (server)|Ice Lake}}, a [[ | + | '''Sapphire Rapids''' ('''SPR''') is [[Intel]]'s successor to {{\\|Ice Lake (server)|Ice Lake}}, a [[7 nm]] [[microarchitecture]] for enthusiasts and servers. |

== History == | == History == | ||

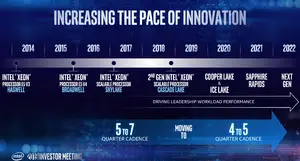

[[File:intel 2019 investor meeting sapphire roadmap.png|thumb|right|Intel Xeon Roadmap through 2021.]] | [[File:intel 2019 investor meeting sapphire roadmap.png|thumb|right|Intel Xeon Roadmap through 2021.]] | ||

| − | Sapphire Rapids was first announced during the May 2019 Intel Investor Meeting. Sapphire Rapids | + | Sapphire Rapids was first announced during the May 2019 Intel Investor Meeting. Sapphire Rapids was planned to succeed {{\\|Ice Lake (Server)|Ice Lake}} in 2021, was however delayed to 2023. |

== Process Technology == | == Process Technology == | ||

| − | Sapphire Rapids is planned to be manufactured on Intel | + | Sapphire Rapids is planned to be manufactured on the Intel 7 process (previously 10nm Enhanced SuperFin (ESF)). |

| + | |||

| + | == Compiler support == | ||

| + | Support for Sapphire Rapids was added in LLVM Clang 12 and GCC 11. | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Compiler !! Arch-Specific || Arch-Favorable | ||

| + | |- | ||

| + | | [[GCC]] || <code>-march=sapphirerapids</code> || <code>-mtune=sapphirerapids</code> | ||

| + | |- | ||

| + | | [[LLVM]] || <code>-march=sapphirerapids</code> || <code>-mtune=sapphirerapids</code> | ||

| + | |} | ||

| + | |||

| + | === CPUID === | ||

| + | {| class="wikitable tc1 tc2 tc3 tc4" | ||

| + | ! Core !! Extended<br>Family !! Family !! Extended<br>Model !! Model | ||

| + | |- | ||

| + | | rowspan="2" | SP || 0 || 0x6 || 0x8 || 0xF | ||

| + | |- | ||

| + | | colspan="4" | Family 6 Model 143 | ||

| + | |} | ||

== Architecture == | == Architecture == | ||

=== Key changes from {{\\|Ice Lake (server)|Ice Lake}}=== | === Key changes from {{\\|Ice Lake (server)|Ice Lake}}=== | ||

| − | * [[ | + | * [[Intel 7]] (from [[10 nm SuperFIN]]) |

* Core | * Core | ||

| − | ** {{\\|Sunny Cove}} '''→''' {{\\| | + | ** {{\\|Sunny Cove}} '''→''' {{\\|Golden Cove}} |

| − | * Memory | + | * New Integration |

| + | ** {{intel|Data Streaming Accelerator}} (DSA) | ||

| + | * Memory | ||

** DDR5 (from DDR4) | ** DDR5 (from DDR4) | ||

| + | ** Optane DC DIMMs | ||

| + | *** Barlow Pass '''→''' Crow Pass | ||

* I/O | * I/O | ||

** PCIe Gen 5.0 (from Gen 4.0) | ** PCIe Gen 5.0 (from Gen 4.0) | ||

| Line 38: | Line 63: | ||

== See also == | == See also == | ||

| − | * {{\\| | + | * {{\\|Golden Cove}} |

| − | |||

Latest revision as of 23:26, 12 November 2022

| Edit Values | |

| Sapphire Rapids µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | 2023 |

| Process | Intel 7 |

| Instructions | |

| ISA | x86-64 |

| Succession | |

Sapphire Rapids (SPR) is Intel's successor to Ice Lake, a 7 nm microarchitecture for enthusiasts and servers.

Contents

History[edit]

Sapphire Rapids was first announced during the May 2019 Intel Investor Meeting. Sapphire Rapids was planned to succeed Ice Lake in 2021, was however delayed to 2023.

Process Technology[edit]

Sapphire Rapids is planned to be manufactured on the Intel 7 process (previously 10nm Enhanced SuperFin (ESF)).

Compiler support[edit]

Support for Sapphire Rapids was added in LLVM Clang 12 and GCC 11.

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| GCC | -march=sapphirerapids |

-mtune=sapphirerapids

|

| LLVM | -march=sapphirerapids |

-mtune=sapphirerapids

|

CPUID[edit]

| Core | Extended Family |

Family | Extended Model |

Model |

|---|---|---|---|---|

| SP | 0 | 0x6 | 0x8 | 0xF |

| Family 6 Model 143 | ||||

Architecture[edit]

Key changes from Ice Lake[edit]

- Intel 7 (from 10 nm SuperFIN)

- Core

- New Integration

- Memory

- DDR5 (from DDR4)

- Optane DC DIMMs

- Barlow Pass → Crow Pass

- I/O

- PCIe Gen 5.0 (from Gen 4.0)

- Platform

This list is incomplete; you can help by expanding it.

See also[edit]

Facts about "Sapphire Rapids - Microarchitectures - Intel"

| codename | Sapphire Rapids + |

| designer | Intel + |

| first launched | 2023 + |

| full page name | intel/microarchitectures/sapphire rapids + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Sapphire Rapids + |