From WikiChip

Difference between revisions of "intel/xeon phi/7295"

(mill) |

|||

| (10 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{intel title|Xeon Phi 7295}} | {{intel title|Xeon Phi 7295}} | ||

| − | {{chip}} | + | {{chip |

| + | |name=Xeon Phi 7295 | ||

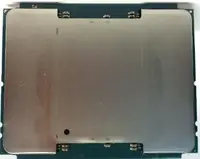

| + | |image=xeon phi knights mill (front).png | ||

| + | |designer=Intel | ||

| + | |manufacturer=Intel | ||

| + | |model number=7295 | ||

| + | |part number=HJ8068303823700 | ||

| + | |s-spec=SR3VD | ||

| + | |market=Workstation | ||

| + | |market 2=Server | ||

| + | |market 3=Supercomputer | ||

| + | |first announced=December 18, 2017 | ||

| + | |first launched=December 18, 2017 | ||

| + | |last order=August 9, 2019 | ||

| + | |last shipment=July 31, 2020 | ||

| + | |family=Xeon Phi | ||

| + | |series=x205 | ||

| + | |locked=Yes | ||

| + | |frequency=1,500 MHz | ||

| + | |turbo frequency1=1,600 MHz | ||

| + | |clock multiplier=15 | ||

| + | |isa=x86-64 | ||

| + | |isa family=x86 | ||

| + | |microarch=Knights Mill | ||

| + | |core stepping=A0 | ||

| + | |process=14 nm | ||

| + | |technology=CMOS | ||

| + | |word size=64 bit | ||

| + | |core count=72 | ||

| + | |thread count=288 | ||

| + | |max cpus=1 | ||

| + | |max memory=384 GiB | ||

| + | |v core min=0.55 V | ||

| + | |v core max=1.2 V | ||

| + | |tdp=320 W | ||

| + | |tcase min=5 °C | ||

| + | |tcase max=77 °C | ||

| + | |dts min=5 °C | ||

| + | |dts max=94 °C | ||

| + | |package name 1=intel,fclga_3647 | ||

| + | }} | ||

| + | '''Xeon Phi 7295''' is a 72-core [[x86]] [[many-core microprocessor]] introduced by [[Intel]] in late [[2017]] specifically designed to [[accelerator|accelerate]] artificial intelligence workloads. This processor, which is fabricated on their own [[14 nm process]] based on the {{intel|Knights Mill|l=arch}} microarchitecture, operates at a frequency of 1.5 GHz with a TDP of 320 W and a turbo of 1.6 GHz. | ||

| + | |||

| + | |||

| + | {{unknown features}} | ||

| + | |||

| + | |||

| + | == Cache == | ||

| + | {{main|intel/microarchitectures/knights_mill#Memory_Hierarchy|l1=Knights Mill § Cache}} | ||

| + | {{cache size | ||

| + | |l1 cache=4.5 MiB | ||

| + | |l1i cache=2.25 MiB | ||

| + | |l1i break=72x32 KiB | ||

| + | |l1i desc=8-way set associative | ||

| + | |l1d cache=2.25 MiB | ||

| + | |l1d break=72x32 KiB | ||

| + | |l1d desc=8-way set associative | ||

| + | |l2 cache=36 MiB | ||

| + | |l2 break=36x1 MiB | ||

| + | |l2 desc=16-way set associative | ||

| + | }} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR4-2400 | ||

| + | |ecc=Yes | ||

| + | |max mem=384 GiB | ||

| + | |controllers=2 | ||

| + | |channels=6 | ||

| + | |max bandwidth=107.3 GiB/s | ||

| + | |bandwidth schan=17.88 GiB/s | ||

| + | |bandwidth dchan=35.76 GiB/s | ||

| + | |bandwidth qchan=71.53 GiB/s | ||

| + | |bandwidth hchan=107.3 GiB/s | ||

| + | }} | ||

| + | |||

| + | == Expansions == | ||

| + | {{expansions main | ||

| + | | | ||

| + | {{expansions entry | ||

| + | |type=PCIe | ||

| + | |pcie revision=3.0 | ||

| + | |pcie lanes=36 | ||

| + | |pcie config=x16 | ||

| + | |pcie config 2=x8 | ||

| + | |pcie config 3=x4 | ||

| + | |pcie config 4=x2 | ||

| + | |pcie config 5=x1 | ||

| + | }} | ||

| + | }} | ||

| + | |||

| + | == Features == | ||

| + | {{x86 features | ||

| + | |real=Yes | ||

| + | |protected=Yes | ||

| + | |smm=Yes | ||

| + | |fpu=Yes | ||

| + | |x8616=Yes | ||

| + | |x8632=Yes | ||

| + | |x8664=Yes | ||

| + | |nx=Yes | ||

| + | |mmx=Yes | ||

| + | |emmx=Yes | ||

| + | |sse=Yes | ||

| + | |sse2=Yes | ||

| + | |sse3=Yes | ||

| + | |ssse3=Yes | ||

| + | |sse41=Yes | ||

| + | |sse42=Yes | ||

| + | |sse4a=No | ||

| + | |avx=Yes | ||

| + | |avx2=Yes | ||

| + | |avx512f=Yes | ||

| + | |avx512cd=Yes | ||

| + | |avx512er=Yes | ||

| + | |avx512pf=Yes | ||

| + | |avx512bw=No | ||

| + | |avx512dq=No | ||

| + | |avx512vl=No | ||

| + | |avx512ifma=No | ||

| + | |avx512vbmi=No | ||

| + | |avx5124fmaps=Yes | ||

| + | |avx5124vnniw=Yes | ||

| + | |avx512vpopcntdq=Yes | ||

| + | |abm=Yes | ||

| + | |tbm=No | ||

| + | |bmi1=Yes | ||

| + | |bmi2=Yes | ||

| + | |fma3=Yes | ||

| + | |fma4=No | ||

| + | |aes=Yes | ||

| + | |rdrand=Yes | ||

| + | |sha=No | ||

| + | |xop=No | ||

| + | |adx=No | ||

| + | |clmul=Yes | ||

| + | |f16c=Yes | ||

| + | |tbt1=No | ||

| + | |tbt2=Yes | ||

| + | |tbmt3=No | ||

| + | |bpt=No | ||

| + | |eist=No | ||

| + | |sst=No | ||

| + | |flex=No | ||

| + | |fastmem=No | ||

| + | |ivmd=No | ||

| + | |intelnodecontroller=No | ||

| + | |intelnode=No | ||

| + | |kpt=No | ||

| + | |ptt=No | ||

| + | |intelrunsure=No | ||

| + | |mbe=No | ||

| + | |isrt=No | ||

| + | |sba=No | ||

| + | |mwt=No | ||

| + | |sipp=No | ||

| + | |att=No | ||

| + | |ipt=No | ||

| + | |tsx=No | ||

| + | |txt=No | ||

| + | |ht=Yes | ||

| + | |vpro=No | ||

| + | |vtx=Yes | ||

| + | |vtd=Yes | ||

| + | |ept=Yes | ||

| + | |mpx=No | ||

| + | |sgx=No | ||

| + | |securekey=No | ||

| + | |osguard=No | ||

| + | |intqat=No | ||

| + | |3dnow=No | ||

| + | |e3dnow=No | ||

| + | |smartmp=No | ||

| + | |powernow=No | ||

| + | |amdvi=No | ||

| + | |amdv=No | ||

| + | |amdsme=No | ||

| + | |amdtsme=No | ||

| + | |amdsev=No | ||

| + | |rvi=No | ||

| + | |smt=No | ||

| + | |sensemi=No | ||

| + | |xfr=No | ||

| + | |mxfr=No | ||

| + | |amdpb=No | ||

| + | |amdpb2=No | ||

| + | }} | ||

Latest revision as of 09:28, 10 May 2019

| Edit Values | |

| Xeon Phi 7295 | |

| |

| General Info | |

| Designer | Intel |

| Manufacturer | Intel |

| Model Number | 7295 |

| Part Number | HJ8068303823700 |

| S-Spec | SR3VD |

| Market | Workstation, Server, Supercomputer |

| Introduction | December 18, 2017 (announced) December 18, 2017 (launched) |

| End-of-life | August 9, 2019 (last order) July 31, 2020 (last shipment) |

| Shop | Amazon |

| General Specs | |

| Family | Xeon Phi |

| Series | x205 |

| Locked | Yes |

| Frequency | 1,500 MHz |

| Turbo Frequency | 1,600 MHz (1 core) |

| Clock multiplier | 15 |

| Microarchitecture | |

| ISA | x86-64 (x86) |

| Microarchitecture | Knights Mill |

| Core Stepping | A0 |

| Process | 14 nm |

| Technology | CMOS |

| Word Size | 64 bit |

| Cores | 72 |

| Threads | 288 |

| Max Memory | 384 GiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| Vcore | 0.55 V-1.2 V |

| TDP | 320 W |

| Tcase | 5 °C – 77 °C |

| TDTS | 5 °C – 94 °C |

| Packaging | |

| Package | FCLGA-3647 (FCLGA) |

| Dimension | 76.16 mm × 56.6 mm |

| Pitch | 0.8585 mm × 0.9906 mm |

| Contacts | 3647 |

| Socket | Socket P, LGA-3647 |

Xeon Phi 7295 is a 72-core x86 many-core microprocessor introduced by Intel in late 2017 specifically designed to accelerate artificial intelligence workloads. This processor, which is fabricated on their own 14 nm process based on the Knights Mill microarchitecture, operates at a frequency of 1.5 GHz with a TDP of 320 W and a turbo of 1.6 GHz.

Contents

Cache[edit]

- Main article: Knights Mill § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions[edit]

Expansion Options |

|||||

|

|||||

Features[edit]

[Edit/Modify Supported Features]

Facts about "Xeon Phi 7295 - Intel"

| full page name | intel/xeon phi/7295 + |

| instance of | microprocessor + |

| ldate | 1900 + |